RESEARCH Open Access

# MAC and baseband processors for RF-MIMO WLAN

Zoran Stamenkovic<sup>1\*</sup>, Klaus Tittelbach-Helmrich<sup>1</sup>, Milos Krstic<sup>1</sup>, Jesus Ibanez<sup>2</sup>, Victor Elvira<sup>2</sup> and Ignacio Santamaria<sup>2</sup>

#### **Abstract**

The article describes hardware solutions for the IEEE 802.11 medium access control (MAC) layer and IEEE 802.11a digital baseband in an RF-MIMO WLAN transceiver that performs the signal combining in the analogue domain. Architecture and implementation details of the MAC processor including a hardware accelerator and a 16-bit MAC-physical layer (PHY) interface are presented. The proposed hardware solution is tested and verified using a PHY link emulator. Architecture, design, implementation, and test of a reconfigurable digital baseband processor are described too. Description includes the baseband algorithms (the main blocks being MIMO channel estimation and Tx-Rx analogue beamforming), their FPGA-based implementation, baseband printed-circuit-board, and real-time tests.

**Keywords:** baseband, MAC, MIMO, processor

#### 1. Introduction

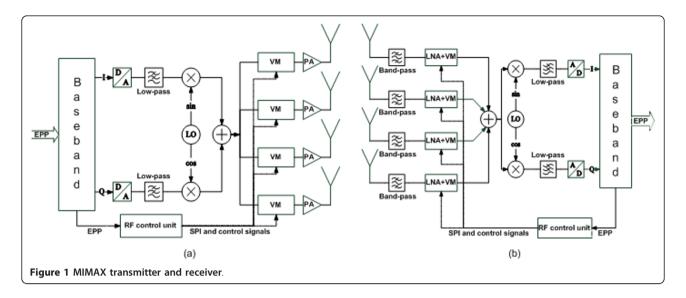

Current multiple-input multiple-output (MIMO) wireless systems perform the combining and processing of the complex antenna signal in the digital baseband. Since complete transmitter and receiver are required for each path, the resulting power consumption and costs of the conventional MIMO approaches [1] limit applications for ubiquitous networks. A low-power and low-cost RF-MIMO (MIMAX) system for maximum reliability and performance (Figure 1) compliant to the IEEE Standard 802.11a [2] has recently been proposed [2-4]. It significantly decreases the hardware complexity by performing the adaptive weighting and combining of the antenna signals in the RF front-end [5-8].

Multiple antennas are used to increase the transmission reliability through spatial diversity. Redesigns have mostly been done in the physical medium-dependent (PMD) layer. They demand for changes in the physical layer convergence (PLC) and medium access control (MAC) protocols to optimally exploit the benefits of the new RF front-end [9-13]. The PLCP pursues mapping MAC protocol data units in PMD layer compliant frame formats. This task is common for all communication schemes defined by the IEEE Standard 802.11.

There are several differences between the MIMAX approach and the full multiplexing MIMO approach. In MIMAX, the same weight is used for all subcarriers in OFDM transmissions, whereas it is possible to weight each subcarrier independently from the others in the full MIMO transmission scheme.

Integrating the signal processing in analogue circuits is limited in the maximum achievable resolution because of noise processes, process variations or nonlinear behaviour of the devices. Therefore, the signal processing has to be calibrated by the baseband to adapt to the RF impairments. This mainly considers the correlation between real and imaginary parts of the vector modulator approach. Compensation is achieved by a calibration performed by the RF control unit in Figure 1. The characteristics of the vector modulator are analysed by this module and stored in an internal memory. The weights provided by the baseband are then transferred into corresponding values of the vector modulator using the previously determined relationship and these new weights control the vector modulator. Integrating

<sup>\*</sup> Correspondence: stamenko@ihp-microelectronics.com

1HP, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany

Full list of author information is available at the end of the article

Furthermore, the spatial diversity must be exploited, possible impairments in the RF spatial processing have to be compensated and the MIMO channel has to be estimated. Particularly, these tasks are not needed in the IEEE802.11a scheme, which is specified for SISO communication.

additional calibration options in the RF front-end and the RF control unit allow an internal adaptation to impairments of the fabrication process and a feedback to the baseband processing. These techniques are based on look-up tables or neural network approaches. The vector modulator is connected to the RF control unit by a serial peripheral interface.

The RF-MIMO analogue front-end (AFE) needs new algorithms to exploit the available spatial diversity of the MIMO channel. Several challenges are addressed in the PLCP. First, the impairments of the RF front-end are considered in the baseband processor. The algorithms must operate reliably and robustly with respect to the limited resolution of the RF front-end. Moreover, these algorithms must determine the optimal complex weights to be applied at each antenna (implemented by means of vector modulators). The MIMO beamforming algorithms need channel state information at both sides of the link, which is obtained by a specific training procedure. Different optimization goals can be used when determining the optimal Tx/Rx weights [6]. Because of its simplicity, the maximization of the signal-to-noise ratio (SNR) is the criterion chosen for implementation.

In order to test the modifications in the IEEE802.11 MAC layer [2], a simulation model of the IEEE802.11 WLAN has been developed in the Specification and Description Language (SDL) [14]. It is composed of simplified models for the 5 GHz OFDM physical layer (PHY), and a detailed model for the MAC layer. The model is used to verify the functional correctness of the MAC design and to investigate the performance.

The MAC processor architecture is presented in Section 2. The hardware accelerator that performs the most time critical MAC functions is described in Section 3. The baseband architecture is presented in

Section 4. Functional modules of the baseband processor are described in Sections 5, 6 and 7. The implementation details are presented in Section 8 and test details in Section 9. The conclusions are drawn in Section 10.

#### 2. MAC architecture

The MAC protocol complies with the IEEE Standard 802.11 and accounts for the following extra requirements due to RF-MIMO technology:

Maintenance of a database of active and available users (MAC address, number of antennas at the user, last optimum weights, etc.).

Configuration of the transceiver's MIMO front end, i. e., the antenna weight coefficients, before sending, or receiving WLAN frames.

Measurement of the channel parameters to determine the optimal weights for every WLAN connection.

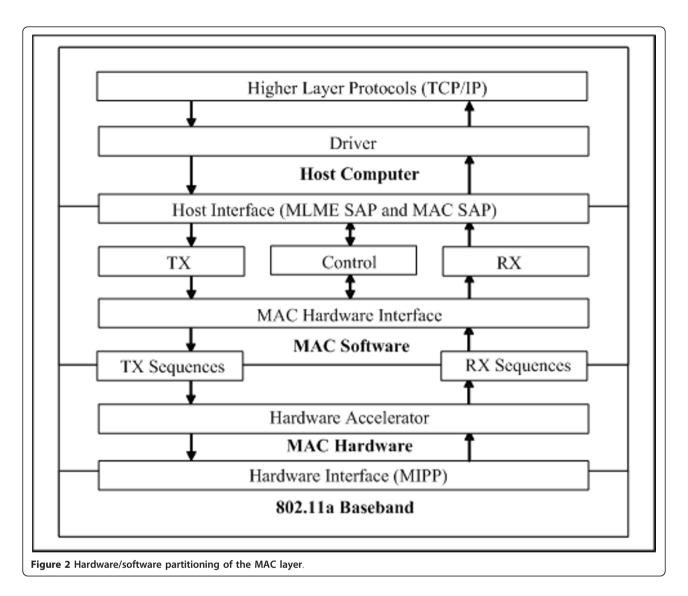

Using the SDL simulation results, a sophisticated hardware/software partitioning of the MAC layer design is carried out to eliminate performance bottlenecks. Finally, the functionalities of transmitting and receiving paths (Figure 2) are assigned to a MAC processor that consists of a general purpose processor (GPP) (MAC software) and an additional hardware accelerator (MAC hardware).

In order to develop a universal RF-MIMO WLAN board independent of any host computer system, we have implemented the complete IEEE 802.11 compliant MAC protocol on the WLAN module. No parts of the MAC need to be integrated into the host driver, which greatly relaxes timing demands within the host computer's operating system. The MAC layer is implemented as hardware/software co-design for a 32-bit GPP and the RF-MIMO specific hardware accelerator.

The software part of the MAC layer generally covers all functionality which is not timing critical or which benefits from great flexibility. This includes maintaining the queue of frames to be transmitted, deferring frame transmissions to stations in power-save mode, frame fragmentation in the transmitter (if desired) as well as de-fragmentation and duplicate detection at the receiver. Also, all the MAC management procedures like scanning, joining, authentication, association, etc., have been programmed in software.

The hardware accelerator functionality for the transmit direction includes a buffer for the next frame, the generation of cyclic redundancy checks (CRC) and an encrypt option. After having sent off the frame, the hardware accelerator waits for the acknowledgement and signals the success or failure (timeout) of the frame transfer to the software. In the receive direction, a CRC checker, a frame address filter, the gene-ration of

acknowledgements and CTS frames and a decryption module are integrated in hardware. Tracking channel state (busy/idle) including back-off for sending frames, 6 timers (32 bit, timer tick 1  $\mu$ s) and the system time (64 bit) are also provided as hardware modules.

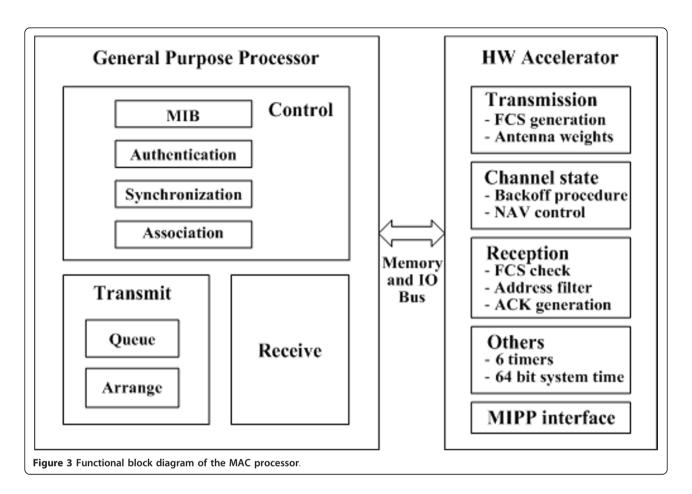

A simplified functional architecture diagram of the MAC processor is shown in Figure 3. The blocks shown in the left part represent the MAC functions executed in software on a 32-bit GPP. The right part sketches the functional scope of the hardware accelerator including an interface between the MAC and PHY layers called MIPP interface [14]. This parallel port interface is a combination of a 16-bit parallel bidirectional data bus and some control and handshake signals.

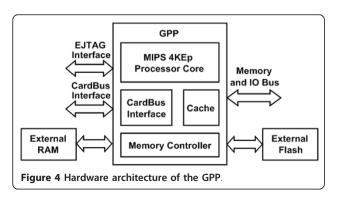

The GPP (Figure 4) is based on a MIPS32 4KEp core with instruction and data caches. All external interfaces including the MAC hardware accelerator are attached to the MIPS processor's memory bus as memory-mapped

I/O components. The processor interfaces comprise a CardBus interface to a host PC, a serial RS232 interface for firmware download, an EJTAG interface with Test Access Port acting as a hardware debugger, and general purpose I/Os.

# 3. MAC hardware accelerator

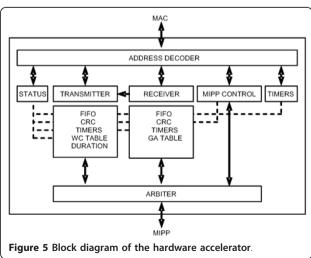

Figure 5 represents architecture of hardware accelerator itself. The MAC interface consists of data bus, address buss and some control signals. There is set of instructions for the hardware accelerator implemented in MAC software. Access to specific modules is provided by the

address decoder. The status register collects any relevant information about processes in other modules and thus allows communication with MAC software. The transmitter module provides functionality for the transmit direction and collision avoidance. The receiver fulfils its natural functionality described earlier. The control component is a broker between MAC and PHY.

All components accessing PHY via the MIPP interface are under the authority of an arbiter block. In order to increase the attainable system throughput, the authors have replaced the standard 8-bit EPP interface with a 16-bit interface.

This section describes details of the most time critical MAC functions and their implementation in hardware. The functionality of the hardware accelerator is defined and verified by simulation within the MAC SDL model. Finally, the hardware accelerator is designed in VHDL and implemented on an FPGA.

The transmitter tracks the channel state (idle or busy). It buffers the next frame and sends it after performing the back-off procedure. In parallel, it generates the CRC. For frames, for which an acknowledgement is expected, it sets a respective timeout and checks for successful delivery. The transmitter block also contains a unit managing the IEEE802.11 Network Allocation Vector which is a mechanism for channel time reservation in the case of frame fragmentation or to solve the hidden node problem in conjunction with RTS/CTS frames.

As a MIMO extension, the transmitter contains a table of antenna weight coefficients for distinct connections. It transfers the respective weight coefficient to the PHY layer before sending a frame. When a frame exchange sequence is finished, it sets some configurable default weight coefficients which should be good enough to receive a short RTS frame from any station. From the source address contained in the RTS frame, the optimal weight coefficients for that connection can be deduced and set in the PHY layer before receiving the (possibly long) frame itself.

The receiver comprises a CRC checker, a frame address filter and the generation of acknowledgements and CTS frames. The control component, as a broker between MAC and PHY, sets and reads the PHY parameters, controls the timers for handshake of the MIPP interface and stores the received data from PHY after any set/write command from MAC.

The arbiter controls the MIPP handshake and the access to bi-directional data bus. A special priority mechanism has been developed to prevent undesired delays in the data flow and raise the data reliability. The priority mechanism is implemented as a state machine driven by signals responsible for:

reset, sending the frame data, sending and receiving the control data and receiving the frame data.

Transmitted data have the highest priority. Then, the control data come. After writing to the MIPP interface, the arbiter automatically will read one word from PHY. This atomic set of instructions prevents from unexpected data loss. Reading of the frame data from PHY

has the lowest priority. Of course, when the reset occurs the state machine will stop for given number of clock cycles and go to idle state.

#### 4. Baseband architecture

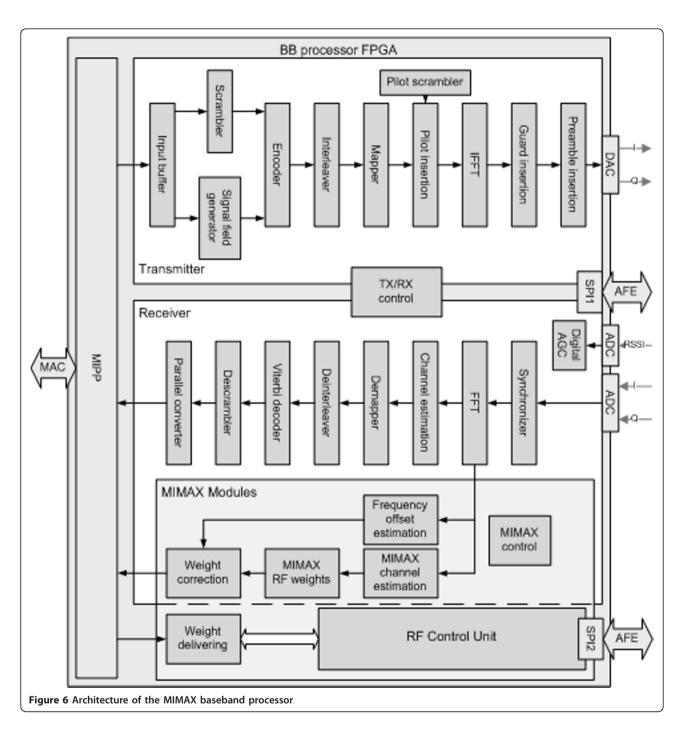

The architecture of the baseband processor is shown in Figure 6. It is composed of two main parts: the baseband processor implementing the IEEE Standard 802.11a and new MIMAX baseband modules implementing new functionalities required by the MIMAX RF front-end architecture.

The new functionalities are grouped into two main modules: channel estimator and MIMAX RF weights (or beamforming) block. These MIMAX modules will be active only when a MIMAX training frame is detected by the Tx/Rx control block, which transfers the MIMAX signal field data to the MIMAX control block in order to start the procedure (i.e. the MIMAX channel estimation and beamforming).

More precisely, the architecture of the baseband processor integrates the following modules:

MIMAX channel estimation: This module estimates the  $n_T n_R$  MIMO channel. The estimation is based on the FFT analysis of the  $n_T n_R$  training OFDM symbols of the received training frame. The  $n_T$  and  $n_R$  parameters denote the numbers of transmit and receive antennas. It works in the frequency domain taking the FFT signal provided by the IEEE802.11a processor as input and uses a least squares estimation method (Section 5).

MIMAX RF weights: It takes the estimated MIMO channel as input and computes the optimal Tx/Rx beamforming weights using the Max-SNR algorithm described in Section 6. It is the most important block in terms of complexity and FPGA resources.

Frequency offset estimation: Due to the residual frequency error at the output of the conventional IEEE802.11a synchronizer, it might be necessary to include a frequency offset estimator working in parallel with the MIMAX channel estimation and RF weights modules (Section 7). To estimate the frequency offset, it is necessary to transmit an additional training symbol, resulting in a training frame of  $n_T n_R + 1$  training symbols.

Weight correction: This module multiplies the weights by a unitary (e.g. rotation) matrix in order to compensate the effects of the residual frequency offset and specific Tx/Rx beamformers used during training.

Weight delivery: It transfers the calculated optimal weights to the MAC processor (the weight updating). In addition, it allows applying (from the baseband) the predefined set of weights during training (the weight setting) and transferring (from MAC) the optimal or default weights during data transmission or reception (the weight uploading).

MIMAX control: This module controls the signal and data flow among all MIMAX blocks. It receives from the Tx/Rx control block information included in the training frame signal field (the number of Tx/Rx antennas, the number of training symbols), as well as some activation and synchronization signals.

RF control unit: This is a control interface between the baseband processor and AFE. It is an integrated part of the baseband processor. All the MIMAX blocks are activated only when a training frame is received. Therefore, they can be powered down while either processing conventional data frames or transmitting training frames. Only the MIMAX control block, the weight delivery block and the RF control unit remain active at any time because it must transfer and set the weights from the MAC processor to the RF control unit.

The complete baseband processor was initially designed using a Matlab model that uses floating-point operations to implement all processing stages. This floating-point model is useful to obtain an upper bound on the expected performance of the baseband processor, but cannot be used for FPGA implementation. A fixed-point Matlab model was then developed that allowed us to take design decisions with regard to the required precision (e.g., number of bits, number of iterations to be applied in the algorithms, etc.).

#### 5. Channel estimation

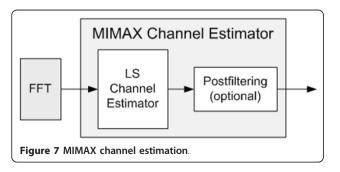

The MIMAX channel estimator uses the  $n_T n_R$  training OFDM symbols included in a training frame. Each training symbol is affected by a specific pair of Tx and Rx beamformers. A conventional least squares algorithm is used to estimate the  $n_T n_R$  equivalent SISO channels at the 52 active subcarriers.

Some design decisions have been taken in order to simplify the implementation of the MIMAX channel estimator. First, the identity matrix has been selected for the Tx and Rx beamforming matrices used during the training stage. Second, the MIMAX training symbols will be the same as the IEEE802.11a long training symbols composed of 52 subcarriers modulated by BPSK values.

As Figure 7 shows, the MIMAX channel estimator works in the frequency domain (i.e. after FFT) and could include an optional post-filtering procedure to smooth the resulting frequency responses. From an implementation point of view, the LS estimator requires very few FPGA resources (just sign inverters and control logic), but the post-filtering process could be expensive in terms of memory and MACs (while providing marginal BER improvement). For this reason, we have initially designed only the LS version of the MIMAX channel estimator block.

# 6. Beamforming weights calculation and delivery

We have focused on the implementation of the Max-SNR beamforming algorithm. This initial algorithm has been chosen because other criteria proposed in [6] use the Max-SNR solution as a starting point.

Furthermore, the choice of the Max-SNR algorithm for implementation simplifies the architecture of this block without significant deterioration of the performance of the whole system. The proposed algorithm reduces to the maximization of the energy of the equivalent SISO channel or, in other words, to the maximization of the received SNR:

$$\underset{w_{T}, w_{R}}{\operatorname{arg\,max}} = \sum_{k=1}^{N_{c}} \left| w_{R}^{H} H_{k} w_{T} \right|^{2}, \quad \text{s.t.} \quad \|w_{T}\|^{2} = \|w_{R}\|^{2} = 1,$$

where the  $n_T n_R$  matrix  $H_k$  is the MIMO channel response at the kth subcarrier, and  $w_T$  and  $w_R$  are the beamformers. These are complex vectors containing the RF weights to be applied by the AFE.

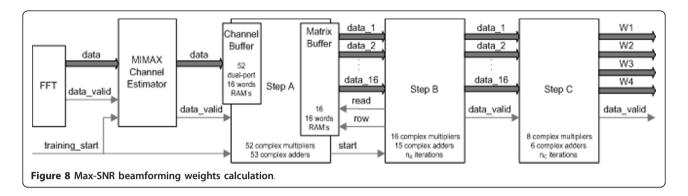

The input signals of the MIMAX RF weights block come from the channel estimator whose outputs are the 52 subcarrier samples for each one of the 16 (considering a MIMAX link with four antennas at the transmitter and receiver sides) equivalent SISO channels. Notice also that all operations are carried out with complex numbers. Specifically, the pseudocode for implementing this algorithm can be summarized in the following steps:

**Step A**: Create 52 column vectors  $x_k$  (dimensions 16  $\times$  1) where the *i*th element of  $x_k$  is the sample of the *k*th subcarrier for the *i*th equivalent SISO channel. Create 52 16  $\times$  16 matrices  $X_k = x_k^* x_k$ . Add the 52 matrices  $\rightarrow Y = \Sigma X_k$

**Step B**: Calculate the dominant eigenvector z of the matrix Y using a fixed number of iterations of a power method.

**Step C**: Construct Z as the  $4 \times 4$  matrix resized from the  $16 \times 1$  vector z. The Max-SNR Rx beamformer  $w_R$  is the left singular vector of Z, which is obtained applying again a fixed number of iterations of a power method.

A schematic diagram of the Max-SNR implementation steps is shown in Figure 8. Step A is creation of the 52 column vectors  $x_k$  where the *i*th element of  $x_k$  is the sample of the kth subcarrier for the ith equivalent SISO channel. The size of  $x_k$  is  $n_T n_R$  (16 in this case). It also creates the 52 rank-one matrices  $X_k = x_k x_k^H$  of  $16 \times 16$  dimension and adds these 52 matrices in a sum Y. Step B calculates the z dominant eigenvector of the sum matrix. The common way to calculate this dominant eigenvector is to perform the singular value decomposition (SVD). However, the implementation of a complete SVD is not needed as it would use too many resources. The alternative solution is the power method which was finally implemented. This method is probably the simplest one for finding the largest eigenvector of a matrix. From the z vector of  $16 \times 1$ dimension obtained by Step B, we construct the Z matrix of 4 × 4 dimension resized by columns. Step C calculates the SVD maximum eigenvector of **Z** in order to extract

the first row of the U matrix. Again, it is not necessary to perform the complete SVD. A beamforming weight coefficient can be calculated as the dominant eigenvector of the product  $ZZ^H$  where  $Z^H$  is the Hermitian of matrix Z. Thus, Step C can be split into two substeps: the first one is a matrix multiplication and the second is a  $4 \times 4$  power method. The resultant vector of this last power method is the  $W_R$  beamforming weight under the Max-SNR criterion.

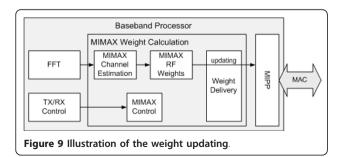

The first task of the weight delivery block consists of transferring the calculated optimal weights to the MAC processor after a training frame has been received. This is so-called weight updating and it is a straightforward procedure (Figure 9). The beamforming weights are provided directly by the MIMAX RF weights block (or by the weight correction block if finally needed).

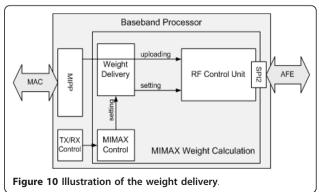

The next task is to transfer the optimal or default weights from MAC to radio-frequency control unit (RFCU) during the transmission or reception of data frames. This procedure, called weight uploading, has easily been implemented by allowing a direct connection between the MAC processor and the RFCU as shown in Figure 10. Finally, the last task is to apply the predefined set of weights during transmission or reception of a training frame: this procedure is denoted as weight setting.

## 7. Frequency offset estimation

Any residual frequency offset that occurs after the synchronizer stage of the conventional IEEE802.11a receiver distorts the weight calculations during training.

Therefore, it could be necessary to estimate and compensate that residual frequency offset by transmitting two training symbols using the same pair of Tx and Rx beamformers. Under assumption that the residual frequency offset is lower than the subcarrier spacing, the maximum likelihood frequency offset estimator is given by

$$\hat{\Delta}f_{\text{ML}} = \frac{1}{2\pi \Delta t} \text{angle} \left( \sum_{k=1}^{Nc} s_1[k] s_2^*[k] \right)$$

where  $N_c$  is the number of active subcarriers;  $s_1$  and  $s_2$  are the OFDM training symbols used for frequency estimation and  $\Delta t$  means the time between symbols  $s_1$  and  $s_2$ .

# 8. Implementation

In this section, the implementation process of the MAC and baseband processors is briefly described. The MAC hardware accelerator has been designed and thoroughly simulated in VHDL. Afterwards, the VHDL model has been implemented on a Virtex5 LX50 FPGA using the Xilinx ISE tool. It is attached to an ASIC that contains the MIPS processor. This FPGA/ASIC solution allows for easy debugging and bug fixing under real-time conditions. The ASIC silicon chip of 50 mm² is fabricated in IHP's 0.25  $\mu m$  CMOS technology [15]. A standalone MAC module in a CardBus form factor with the PCMCIA interface to the host computer and the MIPP

interface to PHY is shown in Figure 11. It consumes the power of 1 W at the operating frequency of 80 MHz.

For design and implementation of the baseband processor, we have used the Xilinx System Generator tool. This tool is a plug-in to the Matlab's Simulink that enables designers to develop high-performance DSP systems to be implemented in FPGA technology. It can automatically translate designs into FPGA implementations that are faithful, synthesizable and efficient.

The chosen FPGA is a Virtex5 LX330 which has 34,560 slices. Regarding the RF weights calculation block, some decisions have been taken to reach a good compromise between FPGA utilization and system performance: We used five iterations for each power method and 8 bits interfaces between the blocks shown in Figure 8. The conventional IEEE802.11a baseband processor occupies around 45%, whereas the new MIMAX baseband modules occupy 33% of the available slices. The operating clock frequency of the processor is 80 MHz.

The baseband modules are integrated in a dedicated baseband board featuring communication with the MAC processor and the AFE. The baseband board incorporates, except a Virtex5 LX330 FPGA, all required interfaces, digital-to-analogue and analogue-to-digital converters for baseband signals, program flash, power and clock circuitries and connectors. The photograph of the produced baseband board is shown in Figure 12.

## 9. Test setups

For testing the PHY and MAC components individually, we have developed two test setups. The first one is

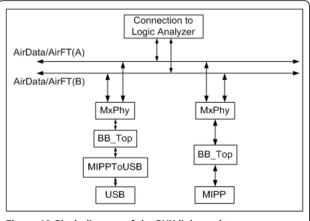

intended for PHY testing without MAC (MAC emulator). This will simplify many test operations like parameter settings since it is not required to "route" them through the complex MAC firmware. The setup consists of a data converter unit (MIPPToUSB in Figure 13) described in VHDL, some small USB hardware to directly connect the baseband board to the USB port of PC (bypassing MAC) and a terminal program on PC to send/receive commands directly to/from the baseband board.

The terminal program has several functionalities that are based on receiving and sending 32-bit words. The format of the words being sent corresponds to the one defined for the MIPPToUSB interface. When starting the program, a menu appears containing the list of all available options. By choosing the adequate command, it is possible to set and read any PHY parameter. In addition, there is a possibility to send a single beacon or training frame or to send frames periodically. Frame parameters, such as the length, data rate, etc., can be selected. Received frames will be displayed and CRC checked. The program is written in C and supposed to be easily extendable for new features or adaptable to debugging problems.

The second test setup (Link Emulator) allows verifying the functionality and evaluating the performance of the MAC implementation including host drivers with an emulated PHY link. The setup provides communication between up to four MAC stations on two independent channels. The interface to the MAC board is generally the MIPP interface described above but, optionally, the

Figure 11 MAC hardware platform.

MIPPToUSB component could be attached providing direct access to PC. The design has been implemented

on a Virtex 1000E FPGA.

The block diagram in Figure 13 shows the structure of the MIPP and USB parts of the Link Emulator. Additional connectors allow to monitor the frames transferred on both channels (AirData and AirFT signals) and some interface signals, e.g. for the USB port, on a logic analyser for debug purposes.

Figure 13 Block diagram of the PHY link emulator.

The MIPP station in the Link Emulator consists of two main components. The first one is BB\_Top which represents the external interface of the baseband processor. It is connected to the MxPhy component, which is responsible for receiving and sending data to the air link. It replaces the MIMAX baseband processor.

The USB station is the extension of a MIPP station with one extra component: MIPPToUSB. Besides that, there are no other changes in comparison to MIPP. Once the data frame is sent from one of the stations, the other stations recognize the incoming frame and receive it. Of course, it is possible to send frames from any of the stations, and it can be received by some or all stations. It is important to say that it is also possible to perform all relevant control and configuration commands for every station.

The baseband board was used for the real-time tests of the MIMAX baseband processor in several setups. First, we have verified the correct reading, changing and re-reading of a few configuration parameters. Then, using the USB terminal program a few beacon, data and training frames were transmitted and the generated I/Q signals at the DAC were analysed to verify a correct transmission. Afterwards, some data frames were generated in Matlab and downloaded to the vector signal generator. The signals generated with the E4438C RF

generator were used as I/Q inputs of the MIMAX baseband board and the correctness of the data was verified by the USB terminal program.

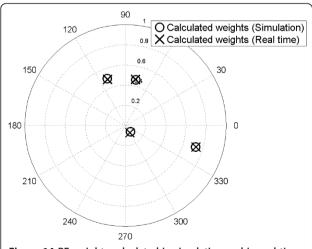

The most important test aimed at checking the correct real-time behaviour of the developed MIMAX modules. For this test, we generated training frames for a 4 × 4 MIMO system where each of the 16 training symbols was affected by a different SISO channel. These training frames were generated in Matlab and distorted by known MIMO channels. The training sequence was transmitted with the vector signal generator and the optimal weights calculated by the processor were provided to the USB terminal program. The beamforming weights obtained in simulation and those provided by the baseband board are compared in Figure 14. This test was repeated for different channel conditions: in all examples, a very good agreement between the weights obtained in simulation and those provided by the baseband board was observed.

A test setup that connects two MIMAX stations with a cable in place of the AFEs has been used to verify the operation and performance of MAC and digital baseband. Each station consists of the following subsystems: a laptop computer running Linux and the WLAN driver software, the MAC board plugged in to the CardBus slot of the laptop and the baseband board connected to MAC via the MIPP cable (Figure 15). This way a system assembling the real MAC layer and digital baseband has been tested in the conditions of an ideal radio channel. MIMO effects cannot be investigated with this setup.

The monitor right in the background of Figure 15 shows the constellation diagram. The video is transferred from the laptop in the back using the 16-QAM signal modulation. The laptop screen in the left displays the received video. One can also recognize the windows of the MIMAX traffic monitor programme (with the

Figure 14 RF weights calculated in simulation and in real time.

yellow and orange bars, which visualize the optimal weight settings) and the terminal programme which controls connection setup and other WLAN parameters.

The primary goal of this test setup is to improve the stability and robustness of the MAC and baseband processors, as well as the WLAN driver software in realtime conditions. Moreover, the signal quality (constellation diagram) and data throughput can be measured for the ideal radio link. The MAC data throughput has been estimated by measuring the time required to copy a large file. The measurement is done at the Linux driver. Thus, it includes the MAC protocol overhead due to frame preambles, acknowledgements and RTS/CTS, the WLAN driver overhead and other limiting effects like MAC firmware performance limitations. Therefore, the measured throughput is expected to be smaller than the nominal PHY data rate. Since the overhead (e.g. frame preambles, duration of an ACK frame) does not scale as the physical data rate increases, the relative throughput degrades very fast with increasing the data rate, which is normal in WLAN [16].

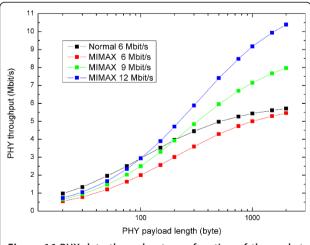

The loss can be overcompensated by the higher physical data rate selected when setting the optimal weights. The simulation results for this behaviour are shown in Figure 16. The black curve shows the normal 802.11 throughput at a physical data rate of 6 Mbit/s as a function of the packet size. The red curve is the MIMAX throughput with RTS and CTS. Due to the additional overhead, this throughput is lower than the normal. However, since the MIMAX technology improves the link quality, allowing for higher physical data rates, the loss due to RTS/CTS overhead is overcompensated for frame sizes above 100 bytes (at 6 Mbit/s). The loss can be further minimized by transmitting several data frames within the RTS/CTS interval.

# 10. Conclusion

In this article, we have described the architecture, design, implementation and test of the new MAC and baseband processors of the RF-MIMO WLAN. These processors fulfil all the requirements of the new AFE that exploits the available spatial diversity of the IEEE802.11a communication scheme.

An efficient cross-layer MAC protocol that utilizes the IEEE 802.11a PHY and RF-MIMO enhancements has been designed. It delivers higher data rate and better link quality than previously realized versions. This article concentrates on design and implementation details of the MAC processor and, especially, the RF-MIMO hardware accelerator as its most important part. The main results of development efforts are the presented hardware/software partitioning scheme and the verified correct processor functionality. Using the proposed hardware accelerator, the maximal data throughput and

Figure 15 Photo of a system assembling the MAC and baseband boards.

Figure 16 PHY data throughput as a function of the packet

reliability of the MAC layer have been reached. In near future, the authors are going to implement the full MAC processor (MIPS GPP and RF-MIMO specific hardware accelerator) as a single ASIC to save energy and space. Even integration with the PHY layer is possible.

A reconfigurable digital baseband processor for an RF-MIMO WLAN transceiver that performs the signal combining in the analogue domain has been designed, implemented and tested. The new baseband processor exploits the available spatial diversity of the IEEE802.11a communication scheme.

#### Acknowledgements

The research leading to these results has received funding from the European Community's Seventh Framework Programme FP7 (2007-2013) under the grant agreement no. 213952 also referred as MIMAX.

# Author details

<sup>1</sup>IHP, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany <sup>2</sup>Communications Engineering Department, University of Cantabria, Plaza de la Ciencia s/n, 39005 Santander, Spain

http://jwcn.eurasipjournals.com/content/2011/1/207

#### Competing interests

The authors declare that they have no competing interests.

Received: 5 July 2011 Accepted: 22 December 2011 Published: 22 December 2011

#### References

- H Boelcskei, D Gesbert, CB Papadias, A-J van der Veen, Space-Time Wireless Systems: From Array Processing to MIMO Communications (Cambridge University Press, Cambridge, 2006)

- IEEE Standard for Information technology–local and metropolitan area networks–specific requirements, Wireless LAN MAC and PHY Specifications, IEEE Std 802.11. IEEE Comput Soc (2007)

- MIMAX: Advanced MIMO systems for maximum reliability and performance http://www.ict-mimax.eu (2008)

- Z Stamenkovic, K Tittelbach-Helmrich, M Krstic, J Perez, J Via, J Ibanez, Architecture of an analog combining MIMO system compliant to IEEE802.11a, in *Proc ICT-MobileSummit 2009*, Santander, Spain, 1–8 (2009)

- F Ellinger, W Baechtold, Adaptive antenna receiver module for WLAN at C-Band with low power consumption. IEEE Microwave Wirel Compon Lett. 12, 348–350 (2002)

- J Via, I Santamaria, V Elvira, R Eickhoff, A general criterion for analog Tx-Rx beamforming under OFDM transmissions. IEEE Trans Signal Process. 58, 2155–2167 (2010)

- 7. R Eickhoff, R Kraemer, I Santamaria, L Gonzalez, Developing energy-efficient MIMO radios. IEEE Veh Technol Mag. **4**, 34–41 (2009)

- A Jahanian, F Tzeng, P Heydari, Code-modulated path-sharing multiantenna receivers: theory and design. IEEE Trans Wirel Commun. 8, 2193–2201 (2009)

- DJ Dechene, KA Meerja, A Shami, S Primak, A novel MIMO-aware distributed media access control scheme for IEEE 802.11 wireless local area networks, in *Proc 32nd IEEE Conference Local Comput Networks*, Dublin, Ireland, 125–132 (2007)

- J Mirkovic, G Orfanos, H-J Reumerman, D Denteneer, A MAC protocol for MIMO based IEEE 802.11 wireless local area networks, in *Proc IEEE Wireless Commun Networking Conference*, Hong Kong, China, 2131–2136 (2007)

- L Yuxia, VWS Wong, Cross-layer design of MIMO-Enabled WLANs with network utility maximization. IEEE Trans Veh Technol. 58, 2443–2456 (2009)

- AM Ashtaiwi, MIMO-aware medium access control, IEEE 802.11 Networks, PhD thesis (Queen's University, Kingston, 2009)

- H-P Loeb, C Sauer, A modular reference application for IEEE 802.11n wireless LAN MACs, in *Proc IEEE Int Conference Commun*, Dresden, Germany, 1–5 (2009)

- Z Stamenkovic, E Miletic, M Obrknezev, K Tittelbach-Helmrich, MAC protocol implementation in RF-MIMO WLAN, in *Proc 16th IEEE Int* Conference Electron Circuits Syst, Yasmine Hammamet, Tunisia, 303–306 (2009)

- Innovations for high performance microelectronics, http://www.ihpmicroelectronics.com

- G Bianchi, Performance analysis of the IEEE 802.11 distributed coordination function. IEEE J Sel Areas Commun. 18, 535–547 (2000). doi:10.1109/ 49.840210

#### doi:10.1186/1687-1499-2011-207

Cite this article as: Stamenkovic et al.: MAC and baseband processors for RF-MIMO WLAN. EURASIP Journal on Wireless Communications and Networking 2011 2011:207.

# Submit your manuscript to a SpringerOpen journal and benefit from:

- ► Convenient online submission

- ► Rigorous peer review

- ► Immediate publication on acceptance

- ► Open access: articles freely available online

- ► High visibility within the field

- ► Retaining the copyright to your article

Submit your next manuscript at ▶ springeropen.com