Hindawi Publishing Corporation EURASIP Journal on Wireless Communications and Networking Volume 2006, Article ID 24853, Pages 1–26 DOI 10.1155/WCN/2006/24853

# Noise and Spurious Tones Management Techniques for Multi-GHz RF-CMOS Frequency Synthesizers Operating in Large Mixed Analog-Digital SOCs

#### **Adrian Maxim**

Maxim Inc., Austin, TX 78735, USA

Received 17 October 2005; Revised 4 May 2006; Accepted 4 May 2006

This paper presents circuit techniques and power supply partitioning, filtering, and regulation methods aimed at reducing the phase noise and spurious tones in frequency synthesizers operating in large mixed analog-digital system-on-chip (SOC). The different noise and spur coupling mechanisms are presented together with solutions to minimize their impact on the overall PLL phase noise performance. Challenges specific to deep-submicron CMOS integration of multi-GHz PLLs are revealed, while new architectures that address these issues are presented. Layout techniques that help reducing the parasitic noise and spur coupling between digital and analog blocks are described. Combining system-level and circuit-level low noise design methods, low phase noise frequency synthesizers were achieved which are compatible with the demanding nowadays wireless communication standards.

Copyright © 2006 Adrian Maxim. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

# 1. INTRODUCTION

The major trend in nowadays wireless transceivers is towards single-chip CMOS integration. Designing low phase noise and low spurious tones frequency synthesizers that operate on the same die with a large and noisy digital core faces numerous system- and circuit-level challenges.

There exist two main mechanisms of parasitic noise and spurious tones coupling to the PLL building blocks: magnetic coupling and electric coupling. The magnetic coupling can appear between two bondwires, between a bondwire and the VCO or the VCO buffer on-chip spiral inductors, or between a bondwire and a metal interconnect line that creates a large magnetic loop. Electric coupling may appear either through the supply lines or via the substrate. Achieving a low phase noise PLL requires a good understanding of all these coupling mechanisms and adopting appropriate circuit- and system-level techniques that result in coupling minimization. A large mixed analog-digital SOC often has several digital supply bondwires that carry large current spikes which may couple to the bondwires providing the supply or signal to the sensitive PLL analog blocks. Increasing the distance between the aggressor bondwire and the receiving one, while ensuring a 90° orientation between them, is the most effective way to reduce the magnetic coupling. One example of critical magnetic coupling is between the bias bondwire of the voltage controlled oscillator (VCO) and any other aggressor bondwire, which may bring a significant variation of the local VCO supply. The nonlinear capacitance connected in parallel with the oscillator's LC tank determines a finite supply pushing gain. Thus the supply noise and spurs are upconverted around the carrier, degrading the VCO phase noise performance. To solve this issue, it has become a standard solution to bias the oscillator from a dedicated high PSRR regulator [1-4]. Another often encountered example is the coupling to the VCO control line in the applications that use an off-chip loop filter [5, 6]. Bringing the sensitive VCO control node off-chip is very dangerous since any magnetic coupling to the corresponding bondwire directly modulates the VCO frequency and thus results in spur and phase noise degradation. This is the main reason that on-chip PLL loop filters are always preferred.

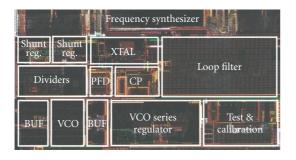

Present design proposes a multiregulator PLL architecture for 802.11 a/b/g SOC applications, in which every single block from the PLL top level is biased from a dedicated series or shunt regulator. These regulators reduce both the impact of bondwire coupling and the parasitic noise and spur coupling between different PLL building blocks. If all analog and digital blocks are built in the same silicon substrate, a substantial noise coupling appears between them. To solve this

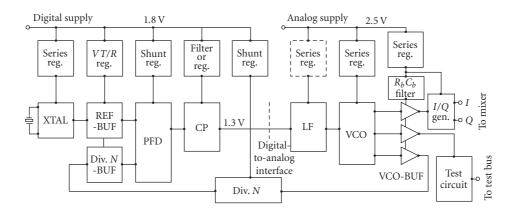

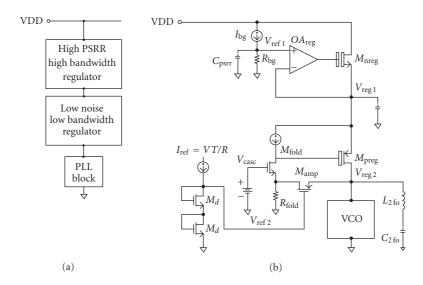

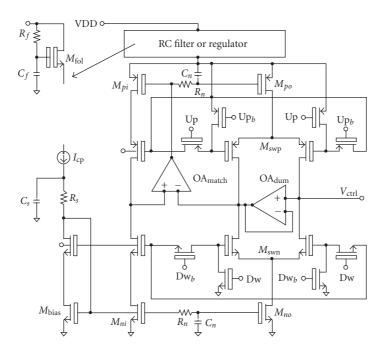

Figure 1: PLL top-level diagram including supply voltage partition and regulation.

troublesome issue, both the sensitive analog blocks and the noisy digital blocks were built in isolated substrates that are separated from the global chip substrate with deep *N*-well layers.

Modern deep-submicron CMOS processes often offer dual gate oxide thicknesses: thin gate oxide FETs that have a high operating frequency and a relatively low breakdown voltage and thick gate oxide FETs that have a medium operating frequency but a much larger breakdown voltage. Present design takes advantage of both device types to optimize the overall PLL phase noise performance.

The signal slew rate assumes very different values in the PLL building blocks (e.g., sinusoidal signal in XTAL oscillator and multi-GHz VCO and square-wave in the clock squaring buffers and the digital dividers). Therefore the impact that a given amount of supply noise has on these blocks can drastically differ. This paper presents a systematic design methodology to select the regulator type and architecture for each PLL building block.

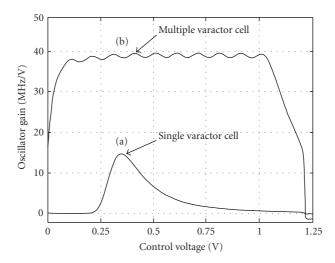

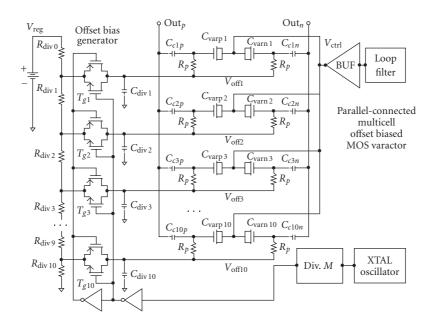

The oscillator is the most sensitive analog block inside the PLL frequency synthesizer. Its tuning gain plays a crucial role in the PLL phase noise performance. The tuning gain needs to be high enough to cover the entire frequency range allocated to the given communication standard and also compensate for the process, temperature, and supply (PTV) frequency variations. The continuous shrinking of the supply voltage in modern deep-submicron CMOS processes, together with the progressive increase towards multi-GHz range of the operation frequency, has resulted in an ever high VCO tuning gain. A large VCO gain results in a degraded PLL phase noise due to a larger contribution of the PLL front-end stages noise and coupled spurious tones. A standard way to reduce the VCO gain is to break the frequency range into several subranges and use for each of them the entire tuning voltage range [3, 4, 7]. This paper proposes a high-resolution frequency calibration network to compensate for process variation, while a virtually constant varactor tuning gain is achieved by using several accumulation MOS varactors connected in parallel and having their C(V) characteristics shifted one from the other, such that the individual gain peaks are distributed over the entire tuning range.

Power supply partitioning and filtering plays a key role in a low phase noise frequency synthesizer. Several low-voltage drop active RC filters are proposed to improve the PSRR of the headroom constrained PLL building blocks. For the cases when using only a filter or a regulator is not enough to provide the required PSRR, a cascade filter-regulator or a dual-regulator architecture was proposed. Most existing PLLs use one [5, 6, 8] or two [3, 9, 10] series regulators to bias the PLL building blocks. This paper presents a multiregulator PLL architecture together with a rigorous methodology to select the optimum regulator architecture for each PLL building block that minimizes the noise and spurious tones coupling when operating in a large mixed signal SOC.

# 2. PLL TOP LEVEL AND POWER SUPPLY PARTITIONING

Figure 1 presents the top-level diagram of the proposed low noise charge-pump PLL, including a crystal oscillator (XTAL) that provides a low phase noise sinusoidal reference clock to the PLL, a reference clock squaring buffer (REF-BUF) that converts the reference sine-wave into a squarewave, the phase-frequency detector (PFD) that compares the phase of the reference and feedback clocks and generates the up/down control signals for the charge-pump (CP), a loop filter (LF) that provides the loop stabilizing zero and reduces the ripple at the voltage controlled oscillator (VCO) control line, the VCO-BUF buffer that increases the edge speed of the multi-GHz output clock, the feedback divider (Div.N) that sets the reference frequency multiplication factor  $(f_{\text{out}} = N^* f_{\text{ref}})$ , and the divider buffer (Div.N-BUF) that drives the second input of the PFD. In addition to these main loop circuits, the PLL also has a quadrature clock generator (I/Q gen.) that performs a divide by two of the VCO output clock frequency and provides two clocks that are precisely at 90° phase difference, and a test circuit that brings at a test pin the signals at different analog and digital nodes from the PLL signal path for debugging purposes.

Investigating the PLL top-level diagram, one may identify two types of building blocks: digital circuits (PFD, Div.N, REF-BUF, VCO-BUF) and sensitive analog circuits (XTAL,

CP, LF, and VCO). Many large mixed analog-digital SOCs are pad-limited, allowing only a single supply (VDD, GND) for the entire PLL. When both the analog and digital PLL building blocks are biased from the same supply line, a particular care needs to be taken in order to avoid the noise and spur contamination of the global supply, which may result in noise coupling between the digital and analog circuits. In low phase noise PLLs it is sometimes critical to avoid also the coupling between two digital blocks. One such example is the noise coupling between the feedback divider (Div.N) that may generate tones that are not harmonically related to the reference frequency and the reference clock squaring buffer (REF-BUF) that can downconvert these tones into the PLL bandwidth, leading to high-level spurs.

Another situation encountered in many applications (presented in Figure 1) is when two supply lines are available to the PLL: one that biases the analog blocks and the second one that biases the noisy digital circuitry. In this case the designer needs to select the optimum boundary between the analog and digital power domains. The best choice for the analog-digital supply domain interface is at a high impedance node where the driving is done in current mode, as is the case for the charge-pump output node. Although the analog charge-pump is placed on the digital supply, using a current mode drive at the boundary between the two power domains, the noise between the analog and digital supplies is prevented from coupling into the signal path, as may be the case when the partition is done at a voltage-driven node (e.g., the up/down PFD output control signals).

The key target of the proposed low noise PLL power supply partitioning is to prevent parasitic noise and spur coupling between the analog and digital blocks. To achieve this, the sensitive analog circuits were biased from high forward PSRR series regulators, while the global supply contamination with digital switching noise was prevented by biasing the digital circuits with shunt regulators that provide a high value reverse PSRR. Starting from the PLL front end, the crystal oscillator does not generate significant supply current spikes. Its bias current is in fact held constant by the automatic amplitude control loop (AAC). Therefore the XTAL oscillator can be biased with a series regulator which does not provide any reverse PSRR rejection. The only reverse PSRR achieved by a series regulator is ensured by its load filtering capacitance. However, the noise and spurious tones reaching the XTAL oscillator and its output buffer (REF-BUF) can seriously degrade the PLL phase noise performance. Therefore a very low noise and high PSRR regulator is required. This paper proposes a novel dual-regulator architecture to bias both the XTAL oscillator and the VCO.

The reference and Div.N buffers dominate the in-band PLL phase noise. Their noise and spurs are directly magnified by the PLL gain (= N). It is therefore crucial to use a very low noise and high forward PSRR regulator for REF-BUF as well. Furthermore, the supply current spikes of the fast switching buffers do not need to be closed directly onto the global supply, since this may cause reference spur degradation through parasitic coupling to other sensitive PLL blocks (e.g., charge-pump and loop filter). A shunt regulator was used to ensure

both a high forward and reverse PSRR rejection. Bandgap referenced regulators usually have a relatively large in-band noise, potentially degrading the REF-BUF phase noise performance through a modulation of its trip point. This design uses a very low noise  $V_T/R$  reference to generate the required PLL low noise reference currents and voltages.

The PFD has a much lower phase noise contribution due to the fact that its clock edges are very fast both at its input and also at its internal nodes. A high edge slope reduces linearly both the impact of the device internal noise and the supply injected noise. Therefore the usage of a regulator is not needed for the PFD from the forward PSRR point of view. However, due to the fact that the required supply voltage for the thin oxide gates (1.3 V) is smaller than the available system supply (2.5 V) and that it is preferable not to close the large current spikes of the fast switching digital gates onto the global supply, a second shunt regulator was used to bias the PFD.

For the charge-pump two contradicting requirements need to be satisfied. On one side, the voltage swing at the CP output needs to be as large as possible in order to reduce the VCO gain and thus decrease the noise and spur coupling from the PLL front end. This requires a high value supply voltage to the charge-pump. On the other side, minimizing the CP spurs downconversion mechanism due to its chopping action requires the usage of a well filtered or regulated local supply that reduces the effective supply voltage available to the CP. A regulator usually takes a much larger headroom in comparison with a simple RC filter ( $2V_{\rm on} + V_T$  for NFET output and  $V_{\rm on}$  for PFET output). Therefore in this design an active RC filter was selected to improve the CP supply noise rejection.

The active loop filters are taking an almost constant supply current in lock conditions, allowing the usage of a series regulator to bias them [4, 11]. However, the presence of a supply line always comes with an elevated supply noise sensitivity. In the case of passive loop filters, there is no need for a regulator as they do not have a supply line. This paper presents a passive feedforward loop filter that significantly reduces the size of the on-chip loop filter capacitance, while requiring no supply line [12].

The VCO is the most sensitive analog block from the entire PLL design. Any supply noise or spur injection that reaches its local supply line is upconverted around the carrier by the supply voltage frequency pushing mechanism [13, 14]. It is now standard to bias the VCO from a dedicated high forward PSRR series regulator [1-4]. The VCO output buffer (VCO-BUF) which squares up the sine-wave looking clock generated by the oscillator leads to high amplitude supply current spikes due to the fast charging and discharging of the load capacitance. However, these current spikes are perfectly synchronous with the oscillator frequency and therefore cannot degrade VCO's phase noise. Hence it is not necessary to isolate the VCO-BUF from the clean analog supply with the help of a shunt regulator, as was done for the other digital blocks. However, the voltage level required by the VCO-BUF and the following I/Q generator that use thin gate oxide FETs is lower than the one used by the VCO (1.3 V

versus 1.5 V), requiring the usage of a separate series regulator. The VCO needs to operate at the maximum amplitude allowed by the device breakdown in order to minimize its phase noise. The device mismatches in the VCO-BUF may result in a significant pulse-width distortion of the resulting square-wave multi-GHz clock. This leads to a large second-order harmonic in the buffer supply current. If this second-order harmonic of the VCO frequency leaks to the I/Q generator, a large I/Q phase mismatch may result. A passive  $R_b$ ,  $C_b$  filter was placed in series with the VCO-BUF supply line in order to close locally to ground its second-order harmonic current.

Finally, the feedback divider (Div.N) that generates most of the internal PLL switching noise is biased from a shunt regulator having a large reverse PSRR, which prevents the contamination of the global PLL supply with tones created by the divider switching. Analyzing the PLL top-level diagram presented in Figure 1, one may conclude that every single building block of the PLL signal path that needs a supply line uses an appropriate filter or regulator. The digital blocks are using shunt regulators that close locally their large supply current spikes, while the sensitive analog blocks use series regulators with large forward PSRR values to minimize the supply and spur injection.

Two supply voltages are available to the present SOC: 1.8 V used by the noisy digital core and 2.5 V used by the analog blocks in the signal path (LNA, mixers, VCOs). The frequency synthesizer uses two dedicated supply lines (see Figure 1). The PLL front end consisting of the digital building blocks (dividers, clock buffers, phase-frequency detector, and switched-current charge-pump) uses the 1.8 digital supply, since the clock edges are enough fast to be insensitive to the residual supply noise obtained after the high PSRR regulators. These digital blocks are built with thin gate oxide FETs that require a no larger than 1.3 V supply. Using a 1.8 V supply and high reverse PSRR shunt regulators results in a power efficiency level around 50%, but offers in return a good rejection of the supply noise and spurious tones.

It is important that the crystal oscillator and the reference clock squaring buffer are connected at the same ground line and there is no potential difference between their local grounds. Any noise voltage between the XTAL oscillator and its REF-BUF buffer may significantly degrade the reference clock phase noise since the slew rate of the input buffer signal (sine-wave) is rather low. A star connection of the two local grounds and a wide metal line (low series resistance) ensures that they are precisely at the same potential. However, biasing the sensitive XTAL oscillator from the noisy digital supply requires a very high PSRR dual-regulator architecture to avoid the supply spur degradation.

Separating the supply of the noisy digital building blocks from the sensitive oscillator prevents the contamination of the supply with reference frequency tones that may degrade the reference spur level. The front-end PLL regulators do not need a large bandwidth, since the noise and spurs coupled at the PLL input are strongly attenuated by the synthesizer lowpass-filter transfer function. This results in lower current levels in regulator's amplifier, improving its power efficiency.

The shunt regulators used to bias the PFD and the PLL feedback divider have intrinsically a significantly lower power efficiency when compared to the series regulators. This is because their DC current needs to be larger than the average digital current in the worst-case process, temperature, and supply voltage corner. A digital calibration of the shunt regulator DC current based on the specific process corner and average die temperature lead to a power efficiency close to 50% even for the shunt regulators. The overall power efficiency of the PLL is around 45%.

The low phase noise reference XTAL oscillator and the output multi-GHz oscillator with their clock buffers need a more complex regulation scheme (two cascaded regulators or one regulator and a cascaded RC filter) to achieve the targeted noise and spur specifications. The XTAL oscillator amplitude is around 0.8 V, allowing the use of a dual regulator within a 1.8 V supply headroom. In contrast the output oscillator amplitude needs to be much larger (3 V peak-to-peak) to achieve a low phase noise, and therefore requires the use of the 2.5 V supply if a dual-regulator architecture is to be implemented. This lowers the power efficiency of the oscillator series regulator below the 50% level.

In an RF frequency synthesizer a lower power efficiency is always traded for better spur and phase noise performance. This gives one of the fundamental performance limitations for the portable application (battery operated) synthesizers. In wired applications the power efficiency is not that strongly constrained, and it is generally sacrificed to achieve a better synthesizer performance. The CMOS process scaling to 90 nm or 65 nm is accompanied by a supply voltage reduction (e.g., to 1 V), reducing the PLL power dissipation. The higher device  $f_T$  leads to faster clock edges and therefore a lower sensitivity to supply noise and spurious tones. This relaxes somewhat the specifications for the biasing regulators, further improving their power efficiency. However, the increase of the operating frequency in emerging wireless application up to 5 GHz, or in some cases beyond 10 GHz diminishes the power saving offered by the CMOS process scaling.

#### 3. SUPPLY FILTERS

One solution to reduce the supply noise and spurious tones injection into the sensitive PLL blocks is to use a supply filter. Their advantages over a regulator are simplicity, smaller voltage drop, and lower die area. Figure 2(a) presents a standard passive RC filter. A first-order RC filter is shown, but higher-order filters can be also used for achieving a sharper frequency roll-off characteristic. In order to achieve an effective supply noise attenuation, it is required that the corner frequency of the filter is with at least one decade lower than the major supply noise frequency spectrum. Often the supply noise can have frequencies as low as few MHz, or even hundreds of KHz, forcing the RC filter corner frequency down to tens of KHz. The main drawback of the passive RC filter is that the DC current of the supplied block passes through the series resistor  $R_f$ . To prevent a severe reduction of the local supply voltage going to the PLL block, due to the supply current variation, a relatively low  $R_f$  value is needed. Usually the

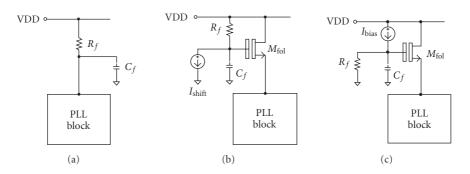

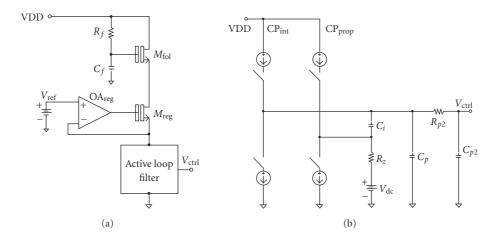

FIGURE 2: (a) Passive RC filter; (b) and (c) active RC filters.

tolerated voltage drop on  $R_f$  is only few hundred mV, resulting in a large  $C_f$  capacitance that can take a significant die area

Active RC filters can be used to solve this problem [3, 4]. They consist as shown in Figure 2(b) of a low corner frequency  $R_f$ ,  $C_f$  filter and an  $M_{\text{fol}}$  source follower. In this case the DC current of the PLL block does not go through the  $R_f$ resistor and therefore a large  $R_f$  value can be assumed. The supply current of the PLL block is provided by the  $M_{\text{fol}}$  active device that follows the filtered gate voltage as the local supply to the load block. The gate leakage of the  $M_{\text{fol}}$  follower is negligible, allowing for  $R_f$  a multi-M $\Omega$  value. The upper limit for  $R_f$  is set by the required noise level at the generated local supply. In circuits with high supply noise sensitivity this may be a stringent limiting factor (e.g., reference clock squaring buffer). The main drawback of the standard active RC filter is the large DC voltage drop equal to  $V_T + V_{on}$  of the  $M_{\rm fol}$  follower. The  $V_{\rm on}$  component can be reduced by using a large W/L aspect ratio for  $M_{\text{fol}}$ . However, this increases its  $C_{\text{gd}}$ parasitic capacitance that in turn limits the high-frequency  $PSRR (PSRR_{HF} = C_{gd}/(C_{gd} + C_f)).$

A more attractive implementation of the active RC filter can be achieved by using native (zero- $V_T$ ) NFETs [11]. In this case the voltage drop on the filter is only a  $V_{\rm on}$  voltage that can be restricted to few hundred mV. Depending on the selected CMOS process, the threshold voltage of the native devices can be either slightly positive or slightly negative. If  $V_T$  is always higher than zero for all process and temperature corners, then the  $M_{\text{fol}}$  device is guaranteed to be in saturation region when diode-connected by the  $R_f$  resistor. However, if the threshold voltage can assume a negative value, then  $M_{\text{fol}}$ will be in triode region, preventing the supply noise filtering  $(M_{\text{fol}})$  is in fact a low value resistance that transfers the noise from the global supply line to the local PLL supply). To avoid the crashing of  $M_{\text{fol}}$ , a small  $I_{\text{shift}}$  current can be drawn out of the  $R_f$ ,  $C_f$  filter, such that the  $V_{GD}$  voltage assumes an enough high negative value to prevent the triode mode operation of the  $M_{\rm fol}$  follower. In many situations the large body effect on  $M_{\text{fol}}$  (their body is the global p-substrate of the die, which is connected to ground) may be enough to guarantee an always positive  $V_T$  for the native NFETs.

Using such an active RC filter built with a native NFET results in a very low-voltage drop (100–200 mV), while providing a PSRR in excess of 40 dB at medium and high

frequencies. However, this circuit does not have any rejection at DC and frequencies lower than the  $R_f$ ,  $C_f$  corner frequency. This may be an issue in the cases when DC-DC converters having significant spurs at tens of KHz are used to bias the SOC. Figure 2(c) presents an alternative architecture for the active RC filter that has a large supply rejection starting from DC. In this case the gate of  $M_{\text{fol}}$  is biased from a voltage achieved by injecting a bias current  $I_{\text{bias}}$  into an  $R_f$ ,  $C_f$  filter. Its main drawback is that the output voltage is set by  $I_{\text{bias}} * R_f - V_{\text{GS}}(M_{\text{fol}})$  and does not track the global PLL supply. In some applications it is beneficial that the additional headroom available at higher supply voltages is provided as extra voltage range to the headroom constrained PLL blocks. However, this last active RC filter architecture is very useful in filtering the local supply to circuits that are sensitive to low-frequency supply noise (e.g., the oscillators).

## 4. BANDGAP AND $V_T$ REFERENCE GENERATORS

Reducing the supply noise injection in a frequency synthesizer operating in a large mixed signal IC mandates the usage of a dedicated regulator for every single PLL building block. An isolation regulator can successfully reject the supply noise and spur injection, but it has noise of its own that may impact the VCO phase noise performance. Achieving a low noise regulator needs a low noise reference voltage generator. The most common way to generate a reference voltage is using a bandgap circuit [1-11]. Figure 3(a) shows a local bandgap voltage replica circuit that uses an  $I_{bg} = V_{bg}/R$  current provided by the V-to-I converter of the master bandgap block that is injected into an  $R_{bg}$  resistor that closely matches the R resistor (in terms of unit resistor cells) used in the master bandgap circuit. Bandgap references have a good process and temperature stability, but come with a large output noise. The wideband noise can be filtered out with an RC filter, at the price of a large required die area due to the high value capacitance necessary to limit the total integrated white (thermal) noise to a low KT/C term. Rejecting the 1/f noise requires a very low corner frequency, which may not be feasible to implement on-chip. This design proposes an alternative way of achieving a low noise reference voltage using a  $V_T$  referenced circuit, as shown in Figure 3(b). The  $M_{ref}$ device provides the reference  $V_T$  voltage, which creates an  $I_{\text{ref}} = V_T / R_{\text{ref}}$  current through the  $R_{\text{ref}}$  resistor. The  $M_{\text{casc}}$

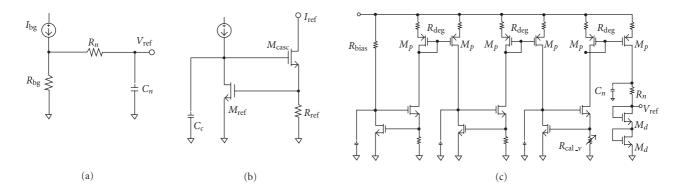

FIGURE 3: Reference circuits: (a) bandgap reference, (b) VT/R reference, and (c) improved PSRR VT/R reference.

cascode device boosts the output impedance of the current generator, helping to improve its PSRR. If enough loop gain is provided to the local feedback loop ( $M_{\text{ref}}$  and  $M_{\text{casc}}$ ), the noise of the output current is dominated by the thermal noise of the  $R_{\text{ref}}$  resistor. Using a large degeneration resistor value reduces the reference current noise at the expense of a low current value. A reference voltage was generated by injecting the  $I_{\text{ref}} = V_T/R_{\text{ref}}$  current into a low impedance load constituted by two diode-connected MOSFET devices  $(M_d)$  as shown in Figure 3(c). The  $V_T/R$  current generator can be biased using either an input current ( $I_{\text{bias}}$ ) or a bias resistor (R<sub>bias</sub>). For a given headroom voltage and current value the noise of a bias resistor is significantly lower than the one of a current mirror (e.g.,  $< 1 \text{ pA}/\sqrt{\text{Hz}}$  for a 20 K $\Omega$  resistor, versus about 6 pA/ $\sqrt{\text{Hz}}$  for a 100  $\mu$ A current source). However, using an R<sub>bias</sub> resistor brings a strong supply voltage dependence of the input current ( $I_{\text{bias}} = (V_{\text{DD}} - 2V_{\text{GS}})/R_{\text{bias}}$ ). This leads to a degraded PSRR of the current generator, increasing the sensitivity to supply noise injection. Three such  $V_T/R$  current cells were connected in cascade to improve the PSRR of the output reference voltage (see Figure 3(c)). Each  $V_T/R$  cell contributes at least 20–25 dB rejection of the input bias current supply dependence, resulting in an overall PSRR well in excess of 60 dB. The PSRR is no longer dominated by the input bias current, but is set by the resistive divider given by the output impedance of the turnaround PFET current mirror  $(M_p)$  and the low impedance of the diodeconnected load devices  $(M_d)$ . Resistive degeneration  $(R_{\text{deg}})$ was used in the PFET current mirrors to reduce its noise contribution and improve the PSRR. The  $C_c$  compensation capacitance provides a dominant pole to the local feedback loop ( $M_{\text{ref}}, M_{\text{casc}}$ ), ensuring a phase margin in excess of  $60^{\circ}$ .

The low noise performance of the  $V_T/R$  current generator comes at the price of a wide process and temperature variation. Optimizing the VCO phase noise performance requires the maximization of the oscillating amplitude, which in turns requires an accurate supply voltage level. A digital controlled resistor  $(R_{\rm cal}_{-\nu})$  was used to calibrate the  $V_T$  referenced supply voltage  $(V_{\rm reg})$  to an accurate bandgap reference. To further reduce the noise and supply sensitivity of the output  $V_T/R$  reference current, a supplementary  $R_n$ ,  $C_n$  noise filter was inserted in series with the output current leg.

#### 5. SUPPLY REGULATORS

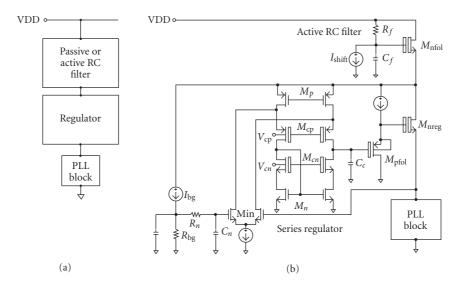

Active RC filters are generally recommended for low current blocks, when simplicity comes on the first place. The relatively large output impedance of the active RC filters  $(1/g_m)$ and also the increased voltage drop at large load currents due to an elevated Von prevents their usage for biasing high supply current blocks. In these situations a regulator is more appropriate for reducing the supply noise injection. However, the regulator requires a larger voltage drop in comparison with a filter. One solution to achieve a high PSRR, while still using a moderate headroom, is using a cascade RC filter and series regulator as presented in Figure 4. The  $R_f$ ,  $C_f$ ,  $M_{\text{fol}}$  active filter helps improving the PSRR of the series regulator at high frequencies (above the regulator's bandwidth), where the PSRR drops sharply. At DC and low to medium frequencies (inside the regulator bandwidth) the active filter is not helping much, most of the PSRR being ensured by the regulator itself.

The series regulator uses a native (zero- $V_T$ ) NFET output device ( $M_{\rm nreg}$ ) to provide the high load current. Reducing the PSRR degradation caused by the  $C_{\rm gd}(M_{\rm nreg})$  was achieved by using a PFET follower ( $M_{\rm pfol}$ ) that drives with a low impedance the gate of the output device. Its bulk needs to be connected at the source in order to avoid the substrate noise injection through the body effect. The  $M_{\rm pfol}$  source follower helps also increasing the headroom available to the folding cascode current mirrors and allows the implementation of the  $C_c$  compensation capacitance with a lower area thin gate oxide NFET. A high gain amplifier is realized with a folded cascode NFET input differential pair (Min).

The reference voltage for the series regulator was generated with an  $I_{\text{bg}} = V_{\text{bg}}/R$  current injected into a matched  $R_{\text{bg}}$  resistor. The  $C_{\text{psrr}}$  capacitor helps improving the PSRR of the reference voltage, while the  $R_n$ ,  $C_n$  filter reduces the noise contribution of the local bandgap voltage generator  $(I_{\text{bg}}, R_{\text{bg}})$ .

Using a cascaded RC filter and regulator, a relatively high PSRR (> 50 dB) was achieved up to frequencies of tens of MHz. This is sufficiently high to reject the supply noise even in high bandwidth PLLs (several MHz). The cascade filter-regulator architecture can be applied to the noise sensitive

FIGURE 4: Cascaded filter and regulator: (a) principle; (b) implementation.

blocks from the PLL front end that have a lowpass or bandpass transfer function to the output clock phase noise.

In high-frequency VCOs the percentage of the tank capacitance coming from the nonlinear device parasitic capacitance is large, leading to a higher supply pushing gain  $(K_{\rm vdd})$  in comparison with the low-frequency VCOs, where most of the tank capacitance is contributed by the linear MIM or metal capacitors. Furthermore, in large mixed signal SOCs the supply voltage is highly contaminated with spurious tones coupled both magnetically and electrically from the switching digital circuits. Using an off-chip filtered supply dedicated only to the low noise oscillator eliminates the board-level noise coupling, but it does not solve the supply noise injection through magnetic coupling between the different IC bondwires. On-chip filtering usually requires a very large die area. Increasing the distance between the sensitive analog pads and the aggressor digital pads and using a 90° orientation between the corresponding bondwires helps reducing the coupling. Flip-chip assemblies can be also used to avoid the bondwire coupling, but at a significant cost increase penalty.

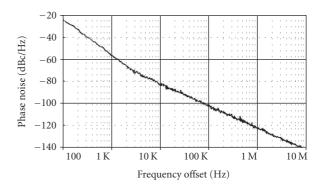

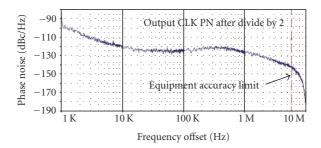

Multi-GHz VCOs have intrinsic supply pushing gains of several MHz/V. Bandgap references come with noise levels around few hundred nV/√Hz. The resulting supply noise injection limits the VCO phase noise to less than 80 dBc/Hz at 100 KHz frequency offset, value that is not acceptable for many modern communication applications. Achieving less than −100 dBc/Hz VCO phase noise at 100 KHz offset requires a supply noise no higher than few tens of nV/√Hz and a supply pushing gain of only few hundreds of KHz/V. In the present application, tolerating a broadband 100 mV peak-topeak supply voltage ripple with a 100 KHz/V supply pushing gain (after supply pushing cancellation) requires a minimum 65 dB PSRR at 1 MHz and in excess of −45 dB PSRR at 10 MHz to achieve the −80 dBc supply injected spur level.

Most existing VCOs use a single regulator to minimize the phase noise degradation due to supply injected noise and spurious tones [3, 5, 10-12]. The oscillator is usually placed inside a phase-locked loop to generate a stable output clock frequency. The PLL feedback loop highpass filters the noise and spurious tones of the oscillator. The corner frequency of the transfer function is PLL's natural frequency  $(f_n)$ . At frequencies lower than  $f_n$  the loop attenuates oscillator's phase noise, while for frequencies higher than  $f_n$  the feedback loop is inactive (open), letting the output clock phase noise follow the VCO phase noise characteristic. Achieving a low supply injected noise and spurs requires a high regulator PSRR up to at least one decade above the PLL's natural frequency (typical up to several MHz, or few tens of MHz). Achieving a large PSRR value at high frequencies requires a large regulator bandwidth, which increases its output voltage noise due both to the reference voltage and the regulator amplifier contributions. This results in a significant degradation of the VCO phase noise through the supply pushing mechanism which upconverts the low-frequency noise of the regulator into phase noise skirts around the multi-GHz carrier. Particularly troublesome is the 1/f noise of the regulator. Once 1/fnoise is created, it is hard to filter, since it requires very large R and C values, which are hard to integrate on-chip. The preference is to use a regulator with low 1/f noise to begin with. Usually the PLL bandwidth is selected to be much larger than the VCO's  $1/f^3$  phase noise corner frequency, such that the 1/f noise upconversion has a small impact on the PLL output integrated phase noise. Strong resistor degeneration was used in the regulator reference voltage circuit to minimize the active device 1/f noise contribution ( $R_{\text{deg}}$  in Figure 3(c)).

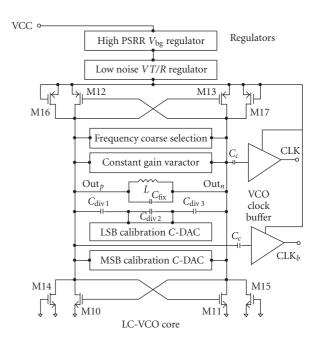

A large regulator bandwidth as required by a high PSRR value comes in contradiction with the regulator's low noise requirement. This paper uses a dual-regulator architecture to bias the VCO [15]. Using two cascaded regulators solves the contradiction between PSRR and noise requirements by distributing the two specifications over the two regulators. Figure 5(a) presents the principle diagram of the dual-regulator architecture. It consists of a first wide-bandwidth

Figure 5: Dual regulator: (a) principle; (b) implementation.

regulator that provides a large value PSRR up to high frequencies, followed by a second narrow-bandwidth regulator that provides the low noise output voltage. Since the noise requirements of the first regulator are relaxed, a standard bandgap voltage reference can be used, as shown in Figure 3(a). In contrast, the second regulator needs to use a very low noise reference voltage, achieved by using a  $V_T$  reference circuit as shown in Figure 3(c). The degraded PSRR of the second regulator at high frequencies is not a concern, since most of the overall PSRR performance of the dual-regulator architecture is ensured by the first wide-bandwidth regulator. Distributing the challenging noise and PSRR specifications between the two regulators results in a PSRR in excess of 60 dB up to tens of MHz, while the output voltage spot white noise is lower than 20 nV/ $\sqrt{Hz}$ .

Figure 5(b) shows the detailed schematic of the dual VCO regulator. Standard  $V_T$  NFETs cannot be used as series devices due to the large resulting voltage drop on the regulator, which leads to a reduced amplitude in the oscillator, with detrimental effect on the phase noise performance. A PFET output device will significantly degrade the PSRR of the first wideband regulator, particularly at medium and high frequencies. To solve the large voltage drop issue of the NFET series regulators, while simultaneously achieving a high PSRR, the first wideband regulator was implemented with a zero- $V_T$  (native) NFET device, which comes at no extra cost in the selected CMOS process.

The bandgap reference voltage for the first regulator was generated by injecting an  $I_{\rm bg}$  current into an  $R_{\rm bg}$  resistor. The  $C_{\rm psrr}$  capacitor improves the PSRR of the reference voltage at high frequencies when the supply noise propagates directly through the capacitor divider given by the  $C_{\rm gd}$  parasitic capacitance of the  $I_{\rm bg}$  current mirror and the  $C_{\rm psrr}$  filtering capacitance.

The second narrow-bandwidth regulator uses a singleended amplifier implemented with the  $M_{\rm amp}$  common-gate stage, followed by the  $M_{\rm fold}$  folding cascode stage. It minimizes the noise of the regulator, while ensuring a large feedback loop gain value. A differential amplifier leads to a larger intrinsic noise when compared with a single-ended implementation, for the same loop gain value. The supply voltage for the oscillator is given by  $V_{\rm SG}(M_{\rm amp})$  and  $V_{\rm GS}(M_d)$ . A digital calibration of the  $V_T/R$  reference current was used to achieve a tight control on VCO's local supply voltage, allowing its amplitude maximization.

The mismatches in the clock path differential buffer create second-order distortion terms. If the second harmonic leaks to the oscillator a further degradation of its phase noise may happen [24]. To avoid this, a high quality factor series LC circuit tuned at the second harmonic of the highest oscillator operating frequency was placed in parallel with the oscillator. In the considered process the highest Q is achieved by the MIM capacitors and the bondwire inductors. Achieving a large rejection factor was possible by using a  $C_{2\,\text{fo}}$  MIM capacitor connected in series with an  $L_{2\,\text{fo}}$  bondwire connected to the package paddle, constituting the ground plane. At lower operating frequencies the  $L_{2\,\text{fo}}$ ,  $C_{2\,\text{fo}}$  circuit shows less attenuation of the second harmonic, but the VCO phase noise is also lower.

#### 6. CRYSTAL OSCILLATOR

The main role of a crystal oscillator is to generate a low phase noise sinusoidal reference clock for the PLL. The operating frequencies of low-end XTALs are limited to 20-40 MHz due to their fundamental tone operation. Overtone crystals can go as high as few hundred MHz, but at a large cost increase. The PLL front-end noise is amplified by the feedback divider modulus (N). In multi-GHz frequency synthesizers the gain can be as high as 40-60 dB, resulting in a large magnification of the reference clock path phase noise. For this reason, it is preferred to use the XTAL with the highest available frequency within the targeted cost range.

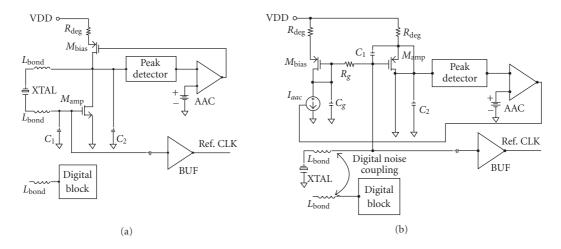

Historically, most of the XTAL oscillators are realized with Pierce configuration (common source amplifier) as shown in Figure 6(a) [3–6]. The main advantage of this

FIGURE 6: XTAL oscillators: (a) Pierce configuration, (b) Colpitts configuration.

architecture is that the two tank capacitors  $C_1$  and  $C_2$  are grounded and can be implemented with MOS capacitors, resulting in a relatively low die area. The bias current for the  $M_{\rm amp}$  amplifier is generated by a resistive degenerated ( $R_{\rm deg}$ ) PFET current source ( $M_{\rm bias}$ ) controlled by the automatic amplitude control loop (AAC). Another advantage of the Pierce configuration is the class C operation of the  $M_{\rm amp}$  device that is ON only at the peak positive amplitude of the generated sine-wave, when the phase noise impulse sensitivity function is at a minimum [13]. This results in a very low phase noise contribution coming from the  $M_{\rm amp}$  device. The XTAL oscillator phase noise is dominated by the crystal tank losses and the bias current source driven by the AAC loop that are always ON (operated in class A).

A standard analog AAC loop consists of a peak detector, a reference voltage generator, and an AAC loop amplifier/comparator [16, 17]. Lower AAC loop phase noise contribution was achieved with a digital implementation in which the output of the peak detector is converted to digital domain by an ADC and the loop amplifier is replaced by a noiseless digital state machine that controls the bias current via a current DAC [18].

The most significant XTAL noise contribution to the PLL output clock phase noise is at low-frequency offsets from the carrier, where the 1/f noise upconversion of the active devices dominates [13, 14]. Therefore from the multitude of Pierce oscillator configurations the lowest phase noise is achieved by the one using an NFET amplifier operated in class C and a PFET bias current source operated in class C (see Figure 6(a)). The justification resides in the much lower C noise of the deep-submicron PFETs (an order of magnitude lower) in comparison with the NFETs.

Implementing the  $C_1$  and  $C_2$  capacitors off-chip is a bad choice in the case of large mixed analog-digital SOCs. This is because the XTAL bondwires may magnetically couple large spurs from the biasing bondwires of the digital circuits which carry high amplitude current spikes. The coupled voltage is divided between  $C_1$  or  $C_2$  capacitors and the  $M_{\rm amp}$  parasitic capacitances. As the last ones are usually much lower in comparison with  $C_1$  and  $C_2$ , most of the magnetically coupled

voltage appears at the gate of  $M_{\text{amp}}$  and therefore at the input of the reference clock squaring buffer (REF-BUF).

The XTAL oscillator generates a sinusoidal signal, while the PLL requires a square-wave clock. A squaring buffer is usually used to accomplish the edge squaring operation. The nonlinear edge squaring performed by REF-BUF buffer is in fact a phase sampling action that results in high-frequency noise and spurs aliasing down into an  $f_{ref}$  interval around the XTAL carrier. Thus the squaring buffer is capable of downconverting into the PLL bandwidth the high-frequency noise and spurs that reach the buffer input. Reducing the amplitude of the coupled spurs at the input of the squaring buffer requires an on-chip implementation of the  $C_1$  and  $C_2$  capacitors. In this case the bondwire coupled voltage is heavily attenuated by the capacitive divider formed with the parasitic pin and pad capacitance added with the PCB capacitance on one side and the on-chip  $C_1/C_2$  capacitors and the amplifier parasitic capacitance on the other side.

From the phase noise perspective using an NFET amplifier is a major drawback for a Pierce oscillator. Furthermore, it requires two bonding pads to connect the crystal, being ill-suited for pad-limited SOC applications. Figure 6(b) presents an alternative way to implement a crystal oscillator using a Colpitts configuration (common drain amplifier). A PFET amplifier  $M_{\text{amp}}$  is used in order to reduce the 1/f noise impact, while a resistively degenerated ( $R_{\text{deg}}$ ) current mirror  $(M_{\rm bias})$  was used to bias the amplifier. The common-mode voltage at the gate of  $M_{\rm amp}$  was chosen close to the supply voltage, such that a class C operation can be achieved, with its dramatic phase noise improvement impact. Moreover, the crystal requires only a single connecting bondwire ( $L_{\text{bond}}$ ), being advantageous for pad-limited SOCs. An  $R_g$ ,  $C_g$  filter was used to minimize the noise contribution of the  $M_{\rm bias}$ device. The main drawback of the Colpitts common-drain configuration is the requirement of a floating capacitance  $(C_1)$  that needs to be implemented either as a MIM or as a metal interconnect capacitance. Therefore it requires a larger die area in comparison with a MOS capacitor. The last ones cannot be used as floating capacitor since their large bottom plate parasitic capacitance gives a high substrate noise

FIGURE 7: Low noise and low coupled spurs reference clock signal path.

injection. The larger die area taken by the Colpitts XTAL is offset by the much lower phase noise in comparison with a Pierce configuration. This results both from a larger oscillation amplitude allowed by a common drain amplifier (only one device versus two stacked devices in the Pierce oscillator) and the reduced contribution of the  $M_{\rm bias}$  noise to the oscillator phase noise.

Another important design choice is the type of FET devices (thin or thick gate oxide FETs) used for both the amplifier and the AAC loop. The thick gate I/O devices can hold a larger voltage (2.5 to 3.3 V), resulting in a larger amplitude with a quadratic impact on the phase noise [13]. Thin oxide FETs can withstand only a 1 to 1.3 V voltage, drastically limiting the oscillator amplitude. However, they have a significantly lower 1/f noise (direct proportional with  $T_{\rm ox}$  oxide thickness), which results in a much lower  $1/f^3$  phase noise.

The spurs coupled to the XTAL local supply are translated near the XTAL carrier through the crystal oscillator supply pushing resulted from the nonlinear capacitance connected in parallel with the crystal [14]. Any spur that appears on the reference clock path is amplified by the large PLL closed-loop gain (equal to the N modulus value inside the loop bandwidth), often resulting as the dominant spur mechanism in the PLL. A dual-regulator architecture was used to achieve a PSRR in excess of 60 dB up to high frequencies (at least one decade above the PLL natural frequency). With 0.5 V voltage drop on each regulator and a 2.5 V global supply, the local supply of the XTAL oscillator comes close to the breakdown voltage of the thin oxide FETs. Therefore both the amplifier with its bias current source and the AAC loop peak detector and amplitude comparator were implemented with thin oxide FETs, benefiting of their much lower 1/f noise.

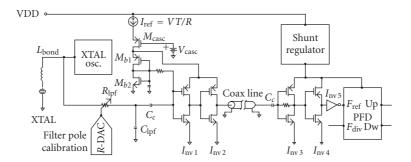

#### 7. REFERENCE CLOCK PATH

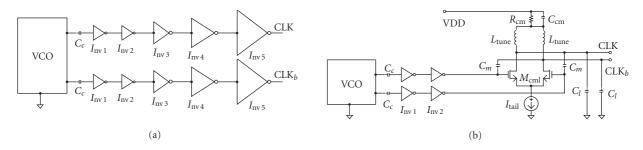

For a low noise PLL it is crucial to achieve a low phase noise edge squaring operation. This is performed by the reference clock buffer presented in Figure 7. As mentioned before, this nonlinear operation is capable of downconverting the high-frequency noise and spurious tones from both the squaring buffer input and its supply line, directly inside the PLL loop bandwidth, where no rejection is presented. This mechanism is particularly dangerous in large bandwidth PLLs when the chance of getting a spur inside the loop band-

width is much higher. Furthermore, large SOCs pose supplementary challenges when they have multiple clock domains that are not harmonically related, opening the path to spur down-conversion due to the nonlinear functions existent in the signal path.

One of the dominant spur coupling mechanisms at the squaring buffer input is through the crystal bondwire. To minimize the spur that arrives at the input of the squaring buffer, an RC lowpass filter  $(R_{lpf}, C_{lpf})$  was placed between the  $L_{\rm bond}$  bondwire and the input of REF-BUF. This attenuates the high-frequency spurious tones before they are applied to the nonlinear edge squaring operation with downconversion capability. To avoid phase noise degradation due to reference clock slewing (which generates noise aliasing), the RC filter should have its corner frequency higher than the PLL reference frequency. Ensuring this condition over all process and temperature corners results in a larger typical corner frequency and thus a lower attenuation of the highfrequency spurs. A maximum attenuation can be achieved by using the lowest possible corner frequency in the RC filter. This design uses a calibrated RC filter that has a resistor DAC to adjust the RC filter time constant, such that its corner frequency stays constant over all process corners and is positioned with one octave above  $f_{ref}$ . The maximum  $R_{lpf}$  resistance is determined by its own noise contribution to the overall PLL phase noise. On the other side, a too low  $R_{lpf}$  resistance results in a very large  $C_{lpf}$  capacitance that may heavily load the crystal tank, potentially reducing its quality factor and thus increasing the XTAL oscillator phase noise.

To avoid large pulse-width distortion in the reference clock path due to differences between XTAL oscillator and squaring buffer common-mode levels, an AC coupling through the  $C_c$  capacitor was used. The DC bias voltage to the input of the squaring buffer is provided by two replica diode devices  $M_{b1}$ ,  $M_{b2}$  and an isolation RC filter. The supply voltage for the front-end inverters of the squaring buffer  $(I_{nv1}$  and  $I_{nv2})$  is provided by an open-loop shunt regulator built with a low noise  $I_{ref} = V_T/R$  current injected into the  $M_{b1}$ ,  $M_{b2}$  replica diode-connected devices. This circuit provides a high forward PSRR to minimize the supply noise and spur injection into the local buffer supply. Changes in the local supply modulate the inverter trip point and thus create jitter. To further improve the PSRR of the shunt regulator, the gate of the  $M_{casc}$  cascode device is referenced to

ground via a  $V_{\text{casc}}$  voltage source, as opposed to the supply referencing used by a standard cascode current mirror, which has a degraded PSRR due to the direct supply noise injection through the  $C_{\rm gd}(M_{\rm casc})$  parasitic capacitance. The shunt regulator offers also a large reverse PSRR which is important for minimizing the reference spur contamination of the global PLL supply due to the large current spikes generated by the fast switching squaring buffer inverters. The reference frequency modulation of the supply given by its effective impedance (set with the on-chip bypass capacitance and the supply bondwire inductance) may couple to other sensitive analog blocks (e.g., loop filter or VCO) and thus degrade the PLL reference spur performance. In present design, for a 50 ps 10-to-90% rise/fall time and a 1.2 V supply the slew rate is 20 GV/s. For such fast reference clock edges a PSRR of only -40 dB is required from the corresponding shunt regulator to achieve output spurs lower than  $-80 \, \mathrm{dBc}$ , when the PLL gain is 50 dB and the supply voltage ripple is 100 mV peakto-peak.

Once the reference clock edges are squared up (have a high slew rate), it is important not to slow them down again before reaching the PFD, since this may create a second noise aliasing point in the reference clock path at the point where the edges are squared up a second time and thus degrade the reference clock phase noise. The first stages of the squaring buffer  $(I_{nv1} \text{ and } I_{nv2})$  need a very low noise supply voltage. Bandgap references are often used to generate supply voltages [1-11]. However, they are notorious for their high noise level which disqualifies them for the reference clock path bias generator. A  $V_T/R$  reference current was used instead (see Figure 3(b)) that has a much lower 1/f and thermal noise due to a large degeneration resistor ( $R_{ref}$ ). Injecting a low noise  $I_{ref} = V_T/R$  current into low impedance diodeconnected FETs, a very low noise supply voltage is achieved. The large process and temperature variation of this voltage is not an issue for the REF-BUF since it tracks the trip point of the squaring buffer inverters.

The internal phase noise of the squaring buffer is dependent on the noise contributed by the NFET and PFET of the first inverter  $(I_{nv1})$  around its trip point, where the edge position is decided. Using a low supply voltage equal to  $V_{Tp} + V_{Tn}$  for the squaring buffer allows only one device to be in strong inversion around the trip point (either the NFET or the PFET). Since the two devices cannot be simultaneously in strong inversion (as is the case for a standard inverter biased from an elevated supply voltage), the phase noise of the squaring buffer is significantly reduced. Using only one device to drive the load capacitance reduces somewhat the edge speed, but the much lower device noise offsets by a large amount the higher noise to phase noise conversion gain due to the lower edge slope.

The PFD is usually operated at the nominal thin gate oxide FET supply voltage (e.g.,  $1.3\,\mathrm{V}$  in a  $0.13\,\mu\mathrm{m}$  CMOS process). Therefore it was biased from a separate closed-loop shunt regulator. A second pair of capacitive coupled inverters ( $I_{\mathrm{nv}3}$  and  $I_{\mathrm{nv}4}$ ) was used to perform the level shifting of the reference clock digital levels and also provide the additional required drive strength. In most crystal oscillators the

phase noise of the rising and falling edges are not identical. For example, in the Pierce oscillator case (Figure 6(a)) the rising edge at the  $M_{amp}$  drain has a lower phase noise since the  $M_{\text{bias}}$  PFET with lower 1/f noise is driving the edge. The falling edge is noisier due to the higher 1/f noise of the  $M_{amp}$ NFET that is driving the edge. For a low noise PLL it is important to select the lower phase noise edge to drive the PFD. A similar situation happens in the Colpitts XTAL oscillator (Figure 6(b)) where the rising edge in the source of  $M_{\text{amp}}$  has lower phase noise. Therefore the Pierce oscillator requires a even number of inverters between the gate of  $M_{\text{amp}}$  and the input of the PFD (assuming the PFD is falling edge sensitive), while the Colpitts oscillator needs an odd number of inverters. If the XTAL oscillator (usually placed in the pad ring) and the PFD are not in close proximity, a coaxial metal shield needs to be used for the reference clock path in order to avoid parasitic coupling to the clean reference signal.

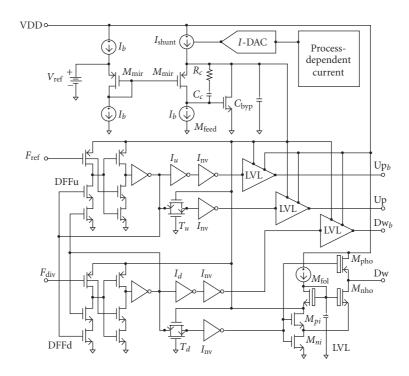

# 8. PHASE-FREQUENCY DETECTOR

The PFD compares the phases of the reference and feedback clocks and generates the up/down digital control signals for the charge-pump. Both its input clocks and the internal node signals are square-waves with high edge slew rate, which minimizes the PFD phase noise contribution (both from internal device noise and the supply injected noise). Minimizing the phase noise contribution of the charge-pump current sources requires the reduction of the time interval that both currents are ON during each reference clock cycle. This also decreases the amount of supply noise and spurious tones that are downconverted by the charge-pump chopping action. To achieve this goal, the PFD needs to have a very fast reset signal propagation time, which requires a minimal number of logic gates in the PFD signal path and also the usage of the fast thin gate oxide FETs.

PLLs that use source, gate, or drain switch chargepump architectures have a relatively slow switching time (few nanoseconds) and therefore require wide up/down PFD pulses to ensure that the charge-pump current sources are active when the phase difference measurement is performed. If the PFD control pulses are narrower than the CP switching time, the so-called dead-zone appears in the PFD-CP transfer function, since the CP does not have enough time to fully switch and thus correct for the phase difference measured by the PFD. The dead-zone in the charge-pump transfer function can seriously degrade the PLL jitter performance, since during this time interval the feedback loop is opened and the clock edges are moving randomly till they generate a phase difference enough large to bring the charge-pump out of the dead zone region. The seven-NAND implementation of the dual D-flip-flop PFD is very popular in CMOS PLLs [1-6]. However, it has a large reset time equal to seven gate propagation times, which typically ranges between 300 pioseconds and 1 nanoseconds depending on the device type and sizes. If a larger reset time is required (several nanoseconds), additional inverters can be introduced in the reset signal path [3].

If the CP transfer function is dead-zone-free, then the PLL reference spurs are reduced linearly with the decrease

FIGURE 8: Phase-frequency detector (PFD) with dedicated shunt regulator.

of the CP pump-up and pump-down pulse widths. The limit to which these pulses can be reduced is set by the CP switching speed. The selected differential current-steering CP architecture provides worst-case switching times as low as 50 pioseconds in 0.13  $\mu$  CMOS. A PFD reset time as low as 100–150 pioseconds was achieved by using thin gate oxide FET dynamic D-flip-flops as shown in Figure 8 [4]. They result in only three gate delays in the reset signal path. The PFD feedback NAND gate that generates the reset signal for the two flip-flops was built within the dynamic flip-flop structure by using the  $M_{\rm rst\,1}$  and  $M_{\rm rst\,2}$  devices. This reduces by one gate delay time the minimum up/down pulse width when the PLL is in lock condition.

The PFD generates single ended up/down signals, while the differential current steering charge-pump requires also the complementary upb/dwb signals. These last ones are generated by adding a parallel path at PFD output, having one more inverter in comparison with the main up/dw signal path. Reducing the glitch current created by the chargepump switching requires a good synchronization of the up/dw and upb/dwb signals. To achieve this, two always-ON transmission gates  $T_u/T_d$  were added in the up/dw signal paths to match the propagation time through the extra inverters  $(I_u/I_d)$  from the complementary upb/dwb signal paths. Reducing the current glitch in the charge-pump requires keeping the common-mode voltage at the NFET differential current steering pair high and the common-mode at the PFET differential current steering pair low, such that at all times there is at least one device in each differential pair that is ON. If at a given moment both devices of the differential current steering pair are turned off due to an un-appropriate common-mode level, a large charge-pump current spike is

generated, which may result in significant VCO control voltage ripple and thus a serious PLL reference spur-level degradation.

To achieve a fast reset in the PFD, thin oxide FETs were used, while a low supply voltage (e.g., 1.3 V) was provided in order to avoid device breakdown. In contrast, the chargepump uses the highest supply voltage available in the system, such that a large oscillator control voltage swing is ensured, as required by a low VCO gain. A level shifter stage need to be introduced between the PFD and the charge-pump, that performs the appropriate digital signal logic-level conversion. Positive feedback cross-coupled differential inverters are often used to perform the level shifting function [1]. Their main drawback is the lower edge speed due to the large gate capacitance of the cross-coupled devices that loads heavily the signal path. Furthermore, positive feedback circuits are notorious for their degraded phase noise and therefore they should be avoided in the low phase noise PLL front end. This design proposes a new level shifter architecture shown in Figure 8 that achieves a much higher edge speed in comparison with the cross-coupled architecture, without using the positive feedback to regenerate the logic level to the higher supply. It consists of a low voltage thin gate oxide inverter  $M_{ni}/M_{pi}$  and a protection high-voltage thick gate oxide current mirror  $M_{\text{fol}}/M_{\text{nho}}$ . For an output Low state the  $M_{ni}$  device is pulling down and the  $M_{\rm nho}$  device operates in triode region, propagating the Low state to the output. The fast thin oxide NFET guarantees a rapid discharge of the load capacitance and therefore a short fall time. For a logic High at the output, the input is in the Low state. Therefore a high voltage thick oxide PFET  $M_{\rm pho}$  can be used to pull-up the output node. A proper sizing of this output PFET is required

to provide a balanced rise/fall time at the level shifter output. The input capacitance of the level shifter is given by the thin oxide inverter and the gate capacitance of the thick oxide pull-up PFET. The last inverter layer in the up/dw/upb/dwb signal paths need to be designed to drive this larger input capacitance of the level shifter, while the level shifter needs to be strong enough to be able to drive safely the input capacitance of the charge-pump switches. The switches size is dictated by the 1/f noise of the differential current steering pair, which sets the W/L aspect ratio for the differential pair devices.

Generating fast edges in the PFD and in its output level shifter requires large supply current spikes that may degrade the PLL reference spur performance if they leak to the sensitive analog blocks (e.g., loop filter or VCO). Preventing the reference ripple coupling through the PLL global supply is ensured by biasing the PFD and its input and output level shifters from a separate shunt regulator that has a large reverse PSRR. An open-loop shunt regulator cannot be used in this case due to its relatively large output impedance that would create a large local supply ripple as a response to the high amplitude supply current spikes. A closed-loop shunt regulator was used instead as presented in Figure 8 [19]. The reference voltage  $V_{\text{ref}}$  is followed at the output through the  $M_{\rm mir}$  PFET current mirror that is kept always active by the  $I_b$  bias current sources. The shunt regulator presents to the global PLL supply line a constant  $I_{\text{shunt}}$  current load. This current either provides the large supply current spikes of the digital circuitry, or it is dumped to ground by the  $M_{\text{feed}}$  local feedback device. An  $R_c$ ,  $C_c$  compensation circuit is used to guarantee a good phase margin of the local feedback loop constituted by  $M_{\text{mir}}$  and  $M_{\text{feed}}$ .

A local bypass capacitance  $C_{\rm byp}$  was added to provide the high-frequency component of the digital load current, while the low- and medium-frequency current components (up to the local feedback loop bandwidth) are provided by the shunt regulator. To guarantee a high reverse PSRR, it is necessary to design the  $I_{\rm shunt}$  DC current to be larger than the highest DC component of the digital circuitry supply current over process, temperature, and supply corners (PTV). The digital circuit presents a very wide range supply current variation over PTV requiring an over-designed  $I_{\rm shunt}$  current. To avoid current wasting in the shunt regulator, the  $I_{\rm Shunt}$  current was set by a current DAC (I-DAC) controlled with a circuit that tracks the process corner of the thin gate oxide FETs, which constitute most of the digital circuitry load capacitance.

## 9. CHARGE-PUMP

The charge-pump (CP) is a key block for a low noise and low spur-level frequency synthesizer. In lock conditions the CP current sources are turned-on for a very short period of time, being OFF for most of the reference clock cycle. Therefore the intrinsic noise of the CP is multiplied in time domain with a periodic rectangular switching function. This corresponds to a convolution in the frequency domain with a discrete sinc spectrum, having the spacing between the tones equal to the reference frequency, while the main lobe width is equal to twice the inverse of the CP on-state time. The 1/f noise of

the charge-pump currents has usually a low corner frequency (few MHz down to hundreds of KHz) which is much lower than the PLL reference frequency (tens of MHz). Therefore the switching action of the charge-pump does not result in aliasing of the 1/f noise. The PLL closed-loop transfer function has a lowpass shape with the corner frequency at the PLL loop natural frequency ( $\approx 0.5\,\mathrm{MHz}$ ). Therefore at the output of the PLL appears only one lobe of the CP 1/f noise spectrum. The 1/f noise power spectrum is attenuated by the square of the switching waveform duty cycle. Hence the CP 1/f noise current (A/ $\sqrt{\mathrm{Hz}}$ ) is effectively scaled down by the duty cycle of the switching waveform.

The charge-pump white noise undergoes aliasing in the frequency domain due to its wide bandwidth spectrum. After piling up the different aliased white noise components (coming from the convolution with each discrete tone from the switching waveform spectrum), they are lowpass filtered by the PLL closed-loop transfer function. As a consequence, the aliasing effect diminishes the noise reduction brought by the switching waveform duty cycle. The noise power is reduced linearly with the duty-cycle, while the equivalent CP output white noise current is reduced by the square root of the duty cycle value. Summarizing, both the 1/f and the white noise originated in the charge-pump can be reduced by minimizing the time interval that the CP is ON (low duty cycle of the switching waveform).

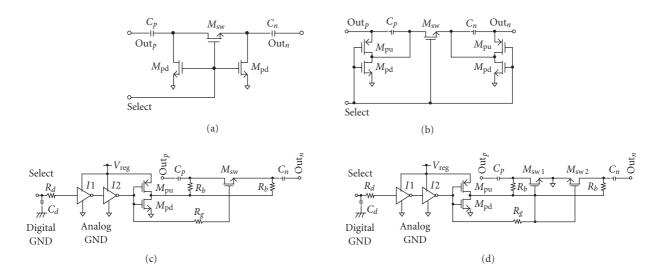

Besides reducing the duty cycle, a second way to reduce CP noise contribution is to minimize its intrinsic noise. The charge-pump is in essence realized by two complementary current mirrors connected to the PLL loop filter high impedance node. In a current mirror both the input (master) and the output (slave) devices contribute noise. If the noise of the output devices  $M_{no}/M_{po}$  is unavoidable, the noise of the input devices  $M_{ni}/M_{pi}$  can be filtered-out by using two very low corner frequency RC filters ( $R_n$ ,  $C_n$ ) as shown in Figure 9. To provide an effective noise filtering, the corner frequency of the  $R_n$ ,  $C_n$  lowpass filter needs to be at least one decade lower than the PLL natural frequency. The value of the  $R_n$  resistor is limited by its own white noise contribution. Therefore large on-chip  $C_n$  capacitors are usually required by the CP noise filters.

Large-area deep-submicron FET filtering capacitors (thousands of  $\mu m^2$ ) come with relatively large gate leakage currents ( $\mu$ A at the maximum IC temperature), which in conjunction with the high  $R_n$  value (M $\Omega$ ) can lead to significant voltage drops (hundreds of mV) that may impact the current mirror ratio. The gate leakage increases steeply with the gate voltage level. In the selected 0.13 µm CMOS process the NFETs have  $I_{g\_leak}=0.1\,\mathrm{nA}/\mu\mathrm{m}^2$  at  $V_{\mathrm{gate}}=1.5\,\mathrm{V}$ ,  $I_{g\_leak}=25\,\mathrm{pA}/\mu\mathrm{m}^2$  at  $V_{\mathrm{gate}}=1\,\mathrm{V}$ , and  $I_{g\_leak}=5\,\mathrm{pA}/\mu\mathrm{m}^2$ at  $V_{\text{gate}} = 0.5 \,\text{V}$  at the room temperature. This issue is even more problematic in further scaled CMOS technologies (e.g., 90 nm and 65 nm CMOS). The leakage currents of the NFETs and the PFETs do not track over process and temperature. PFETs tend to have lower leakage currents, which may lead to a large mismatch between the pump-up and pump-down current. The PLL loop responds in lock conditions by introducing a static offset between the reference and the feedback

FIGURE 9: Dynamic current-matching charge-pump with supply and bias noise filters.

clocks. The equilibrium point is reached when the charge injected by a wider pulse, low value pump current is balanced with the charge injected by the narrow pulse, higher value complementary pump current. The large duty cycle of one of the charge-pump currents determines a significant degradation of the CP noise contribution, and if the wider pump current is the PFET one, then it also increases the supply noise and spur injection. To avoid gate leakage induced current mismatches, the  $M_{ni}/M_{no}$  and  $M_{pi}/M_{po}$  are implemented also as thick gate oxide devices, which have a negligible gate leakage current. Large-area devices were used to reduce their 1/f noise component.

A unity gain buffer  $OA_{dum}$  is usually used to keep the dummy side of the current steering charge-pump at the same potential with the active output (loop filter side). This minimizes the charge-sharing from the dummy side and thus reduces the ripple on the loop filter due to sharing current glitches when the output switches are ON. The noise of this buffer is first sampled on the parasitic capacitances from the common source points of the differential current steering switches when the dummy switches are ON, and is then shared with the loop filter when the output switches are ON. To minimize the  $OA_{dum}$  noise contributions a very large ratio needs to be maintained between the loop filter capacitance and the parasitic capacitance at the common source node.

Reducing the pump-up/pump-down current mismatches is key for a low reference spur level. A dynamic current matching feedback loop was implemented by adding the OA<sub>match</sub> amplifier to drive the gates of the PFET current mirrors such that the NFET and PFET currents are well balanced [19, 28]. The ripple from the dummy side of the charge-pump (followed by the OA<sub>dum</sub> wide-bandwidth operational amplifier) does not modulate the charge-pump PFET cur-

rent since both the  $R_n$ ,  $C_n$  filter and the low  $OA_{match}$  bandwidth are strongly attenuating it. The dynamic charge-pump current matching circuit consists of two feedback loops: a negative feedback given by  $OA_{match}$  and  $M_{pi}$  and a positive feedback given by  $OA_{match}$ ,  $M_{po}$ , and  $M_{swp}$  with  $OA_{dum}$  buffer. The low impedance provided by  $OA_{dum}$  buffer at the inverting input of the  $OA_{match}$  operational amplifier guarantees that the negative feedback has a much stronger loop gain in comparison with the positive one.

Maximizing the voltage swing at the charge-pump output requires the reduction of the number of stacked devices in the NFET and PFET current mirror legs. Cascode tail current mirrors are preferred for their much larger output impedance and thus a lower up/down current mismatch due to the variation of the loop filter voltage. However, cascode current mirrors take a larger voltage headroom that adds to the voltage drop on the ON-state switch to give the minimal output voltage level. Present design proposes a much higher output voltage swing charge-pump in which the  $M_{\text{swn}}$ and  $M_{\text{swp}}$  switches are operated between OFF and saturated ON states, such that they act as cascode devices when they are ON. The current steering operation is determined by the state of the two switches connected to the gates of the differential pair, providing either the cascode bias to the gates of  $M_{\text{swn}}/M_{\text{swp}}$  devices, or connecting them to ground. Eliminating one device from the stacked telescopic architecture of the charge-pump is particularly advantageous for the high charge-pump currents applications.

The noise coming from the supply lines is also sampled by the low duty-cycle switching waveform, determining a reduction of its power. Similar to the charge-pump devices internal noise, the supply injected white noise suffers aliasing, while the supply 1/f noise does not. If a supply filter or a

regulator is used to bias the charge-pump, its 1/f and white noise need to be carefully looked at.

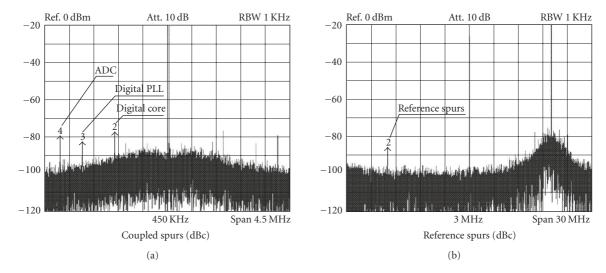

A second concern for a charge-pump is its spur down-conversion capability. The switching action of the charge-pump switches has a chopping operation that results in a frequency translation (mixing). Therefore the high-frequency spurious tones present on the charge-pump supply voltage or bias current are downconverted around the  $f_{\rm ref}$  PLL reference frequency. The resulting low-frequency ripple of the VCO control voltage determines spurs around the multi-GHz output clock. If these spurious tones fall inside the PLL bandwidth, where no rejection is presented by the feedback loop, they are simply amplified by the large N feedback divider modulus. In PLLs having low XTAL frequencies and high output clock frequencies (large frequency multiplication factor), these spurs may be the dominant spur mechanism.

The charge-pump presents this mixing property both to the supply voltage and the input bias current high-frequency spurious tones. The  $R_n$ ,  $C_n$  CP noise filters also help rejecting the high-frequency spurs coming from the bias current. If additional rejection is required, a supplementary filter  $R_s$ ,  $C_s$  can be added in series with the input bias current ( $I_{\text{bias}}$ ). To minimize the supply ripple, an RC filter or a regulator can be used to bias the charge-pump. Reducing the VCO gain requires the maximization of the voltage swing at the CP output (1.3 V for thin gate oxide FETs). Using a regulator to bias the CP takes at least 0.5 V of headroom, which may be too much, particularly in the low-voltage applications. This design uses an active RC filter built with a zero- $V_T$  NFET, which takes only 200 mV of voltage headroom and provides in excess of 40 dB of rejection for the high-frequency supply spurious tones. In this application the 1.8 V digital supply is sufficiently high to accommodate a 0.2 V voltage drop on the active filter and the 0.3 V headroom required by the PFET cascoded charge-pump current source.

#### 10. LOOP FILTER

The main functions of the loop filter are to provide the PLL stabilizing zero and to filter the ripple on the VCO control voltage. Passive RC filters are widely used [2, 5, 6] due to their simplicity and their excellent power supply noise rejection. A passive loop filter has no supply lines, the only supply injected noise is coming from the charge-pump supply line. This is minimized by ensuring a CP output impedance much larger than the loop filter impedance at the spur frequency. The major drawback of the passive filters is their large capacitor size, particularly in low PLL bandwidth applications. These capacitors are often implemented off-chip, increasing the external component count and exposing the sensitive VCO control line to parasitic magnetic coupling due to the connection bondwire and package lead [5, 6]. Active loop filters were used to reduce the size of the loop filter capacitor [19, 21, 22]. A further reduction was brought by implementing a Miller capacitance multiplication technique [1]. This magnifies the size of the physical loop filter capacitance, allowing the on-chip realization of a large PLL time constant. However, the Miller capacitance gain comes also